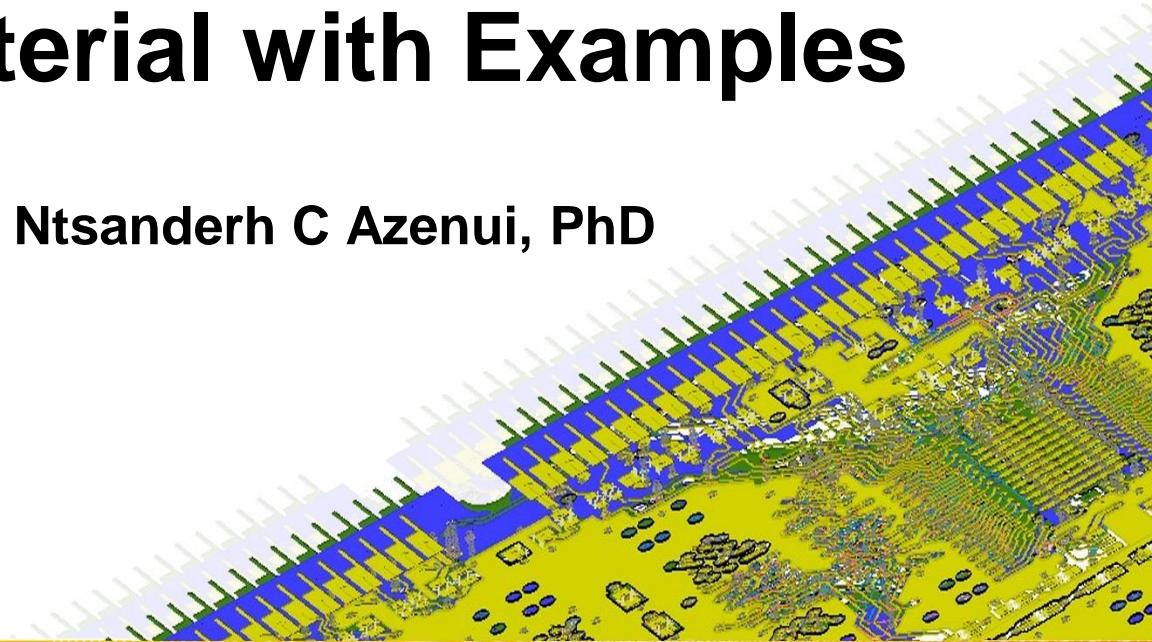

## SIwave-CPA

# Training Material with Examples

Ntsanderh C Azenui, PhD

# Legal Disclaimer

- **ANSYS product information is highly confidential and proprietary. By proceeding with ANSYS product discussions, recipients agree not to use or disclose this information for any purpose.**

- **ANSYS product information is not a binding commitment, and is subject to change in ANSYS' sole discretion. ANSYS undertakes no obligation to update product information.**

- **Purchase decisions, investments and other actions should not be taken in reliance on ANSYS product information, which may be prospective in nature, forward-looking and not guaranteed to occur.**

# CPA (Chip-Package-Analysis) solver

## Solver Features

- FEM quasi-static field solver. Geometry driven mesh. Uses multi-threading (HPC)

- CPA MoM (activate Q3D solver feature) uses Adaptive Meshing

- Fast, accurate **RLGC** extraction of power & signal nets for IC, Packages and PCB

## Usability Features

- Pin group, or Per-bump-(up to thousands)-resolution SPICE models including decoupling caps and inductors

- High Resolution graphical color maps of R and L for package probing

- IBIS RLGC Model Generation

- Scalability (handles large number of nodes, eg. 5000)

- Chip + package co-design either in Siwave or Redhawk with CPM file addition

# Applications

- **Package/PCB electrical engineers:**

- RLCG extraction of RDL, PKG and PCBs (DC RL, and frequency dependent AC RL and CG)

- User selectable solver choices (FEM or Q3D-MoM solvers)

- Probe the layout weakness – do design iterations – PDN system – DC to GHz's – individual bump level – fast turn around

- *SI analysis – quick extraction of 100's of signals – IBIS model generation of RLCK – quick scan of signal properties*

- *PCB RLCG modeling including the passive RLC components*

- *Broadband S-parameter export from RLCG data*

- **Chip engineers:**

- Include the package effects into Chip simulations – cosimulation of chip+pkg – hotspots – codesign – covisualization of results

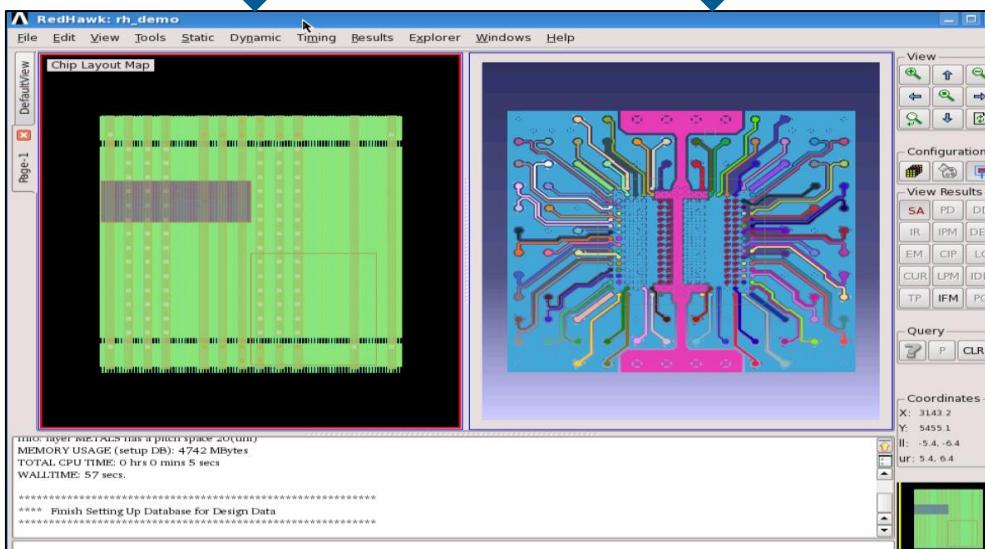

# Chip-Package Coanalysis and Codesign

RedHawk and Totem

*Chip data*

*Pkg data*

Slwave-CPA

- CPA model generation in Slwave.

- Model exchange into RedHawk for cosimulation and covisualization of results.

# SIwave-CPA Highlights

## Technology

- Uses 3D FEM and 3D MoM solvers

- Similar to PSI and Q3D solvers

- Extracts RLCG netlist

- Frequency dependency

- Ground bounce preserved

## Performance/Capacity

- Very high capacity FEM solver – full package and PCB structures – 10,000's of sources/sinks

- Fast extraction (minutes to a few hours – even for extremely large packages with over 10K bumps)

- Distributed computing (HPC)

## Accuracy

- PDN analysis with FEM solverSelect MoM solver (Q3D) for better accuracy.

- Performance-Accuracy trade-off

## Applications

- Silicon Interposer and RDL

- Thru Silicon Via (TSVs) structures

- Packages

- PCBs – Power Electronics

- Supports decaps, and embedded components

- PI and SI analysis

- IBIS modeling

- Wideband Spice models

## System Flow and Usage

- Integrated into Ansys Chip tools

- Integrated into Ansys SIwave

- Very easy to use and detailed reports

# R19 SIwave-CPA Highlights

## Solvers

- Fast RLCG extraction at per-bump level with high granularity

- Rigorous MoM solver (Q3D) for high accuracy applications

- Distributed computing (HPC)

## Models

- Broadband Spice netlist and IBIS model generation

- ESD and CPA models for ANSYS RedHawk/Totem Chip-Pkg-System cosimulations

## Results

- Detailed reporting capabilities including:

- RLCG spreadsheets

- Pin level color maps of resistance and inductance

- Spice netlist's compatible with all mainstream Spice simulators

- HTML reports including the complete setup, geometry, and the results. Interactive control of results in the report for customization.

# R19 SIwave-CPA Highlights

## Flexible Source/Sink Setup

- Traditional CPA setup (Die, BGA and PDN components)

- RedHawk generated PLOC import

- Chip Power Model (CPM) import

- Individual source/sink setup, with ability to float pins

## Flexible Choices

- User-defined extraction frequency (both FEM and MoM solvers)

- Independent selection of DC RL, AC RL and CG extractions for Q3D

- A new fast and robust mesher coupled with adaptive refinement

- Ground planes above and below the structures supported for Q3D

# CPA-Q3D: HPC Performance

| Project name                              | Machine number | Total Runtime (H:M:S) | Peak memory(MB) |

|-------------------------------------------|----------------|-----------------------|-----------------|

| (30 nets + 72 source ports)               | 1              | 1:36:51               | 13080           |

|                                           | 2              | 0:50:31               | 9716            |

|                                           | 4              | 0:44:09               | 8862            |

|                                           | 8              | 0:23:15               | 8516            |

| (77 nets + 211 source ports)              | 1              | 1:06:45               | 9696            |

|                                           | 2              | 0:30:08               | 8787            |

|                                           | 4              | 0:21:38               | 8226            |

|                                           | 8              | 0:16:55               | 7274            |

| (38 nets + 97 source ports)               | 1              | 0:58:28               | 12512           |

|                                           | 2              | 0:39:10               | 9260            |

|                                           | 4              | 0:29:07               | 8474            |

|                                           | 8              | 0:24:55               | 8206            |

| wirebond<br>(230 nets + 230 source ports) | 1              | 1:09:40               | 9995            |

|                                           | 2              | 0:31:06               | 9957            |

|                                           | 4              | 0:19:56               | 9708            |

|                                           | 8              | 0:15:16               | 8487            |

note:

Each machine uses 8 cores

Peak memory is for master node

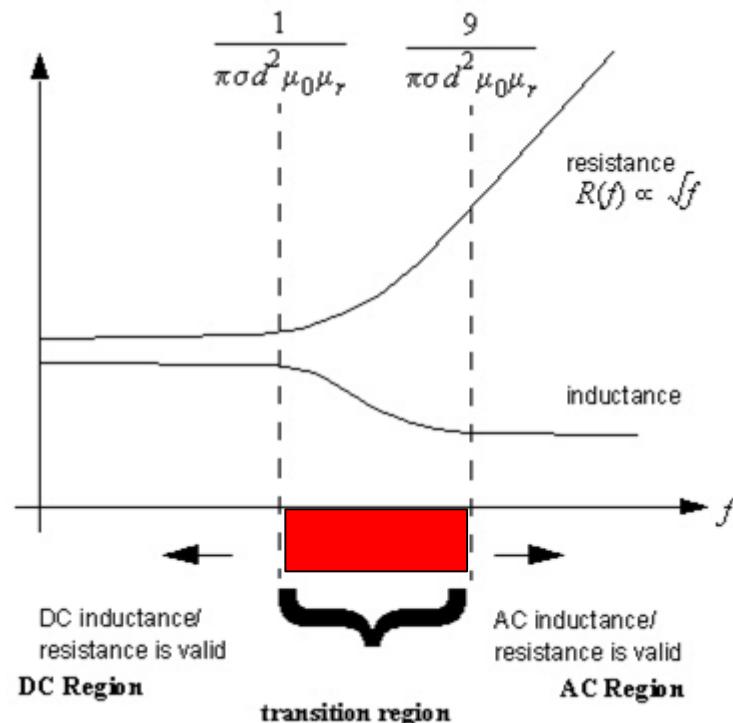

# Some Key Technical Details of CPA solver

- Quasi-static approx. is a simplification of Maxwell's equation for electrically small structures. Rule of thumb: “**structure size < lambda/10**” at maximum freq. of interest

- Depending on the options selected for “**Select Parameters to Compute**,” CPA

- Solves (CG & RL) at DC

- Solves (CG & RL) at AC using the entry for “**G+RL frequency**” as the solution frequency

Surface current (skin depth) is well developed, and **quasi-static approx.** (structure size<lambda/10) holds

- Blends AC and DC solution in the transition region

$d$  is conductor thickness

- The Quasistatic approx. allows to solve Poisson equations for the electric and magnetic potential functions **Phi** and **A**

- $V = \text{grad}(\Phi); \text{grad}^2(\Phi) = \rho; \text{grad}^2(A) + k^2 A = J$

- where  $V$  and  $J$  are the excitations

- The charge,  $Q$  is then derived from **Phi** and find CG from  $(G + j\omega C)V = j\omega Q$

- $R$  and  $L$  derive from the surface current distribution, the surface impedance  $Z = \sqrt{2j}/(\sigma\delta)$ , and **A**

$$Z = R + j\omega L$$

# CPA – FEM Solver

- FEM Solver is based on 3D modeling – similar to SIwave-PSI solver

- Geometrical objects such as microstrip/striplines, vias, pads, etc. are all modeled as volumetric metallic objects with finite conductivity

- Volumetric elements (Prisms) are placed inside the via barrels, traces and shapes

- Dielectric objects are modeled as such using 3D elements with lossy material

- FEM solution assumes that RL and CG are decoupled in the quasi-static limit and can be extracted separately.

- This is similar to MoM approach of Q3D solution.

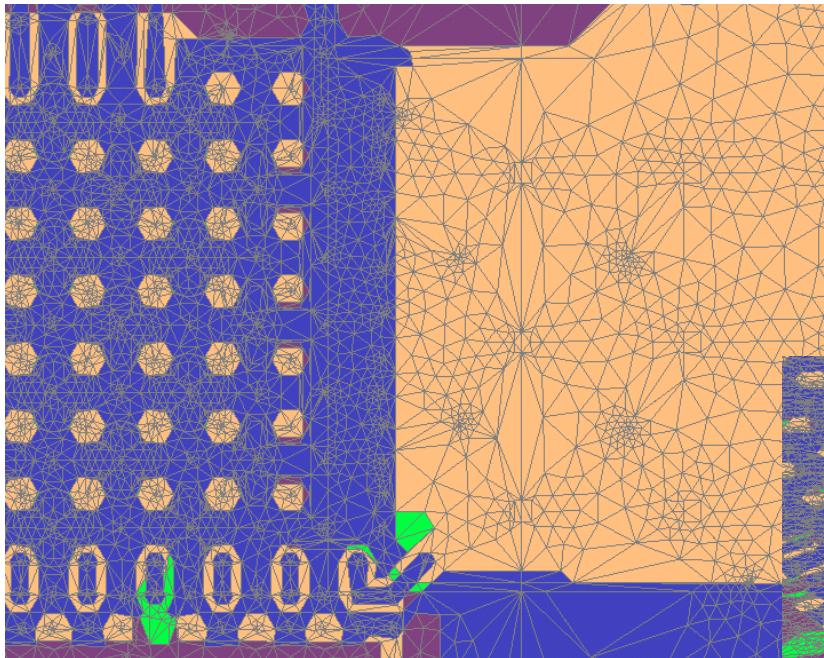

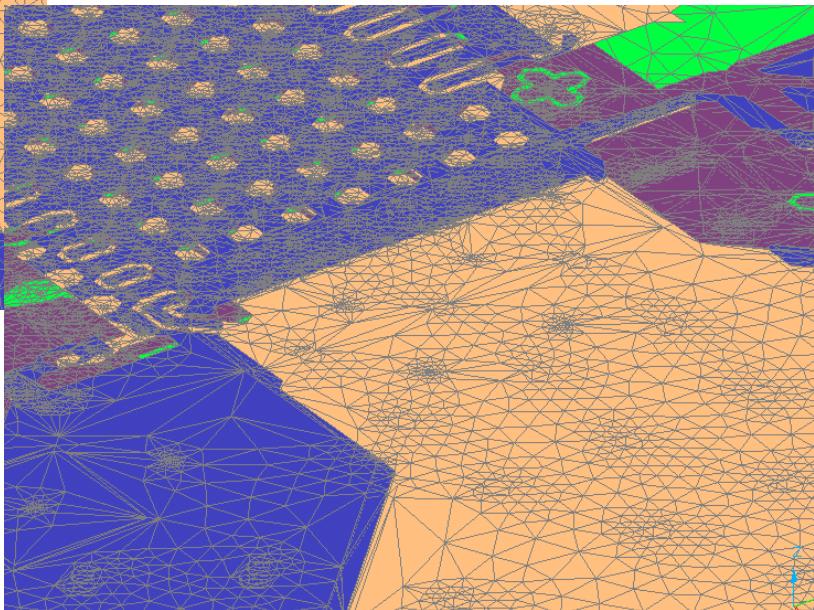

# FEM Meshing: Fast Conformal Meshing

- Conformal composite mesh elements

- Identification of domains and key geometry areas

**Mesh technology is critical for high capacity simulations. Proper use of higher-order elements helps in controlling number of unknowns.**

# FEM Solver: Key to a Fast RLCG Extraction

- **Sparse nature of FEM matrices**

- **Mature technology of the fast Sparse matrix solver**

- **Direct matrix factorization – Only once**

- **Forward-Backward substitution for multiple right-hand-sides (1000's of RL branches) – very fast extraction of per-pin RL**

- **Highly multi-threaded solver**

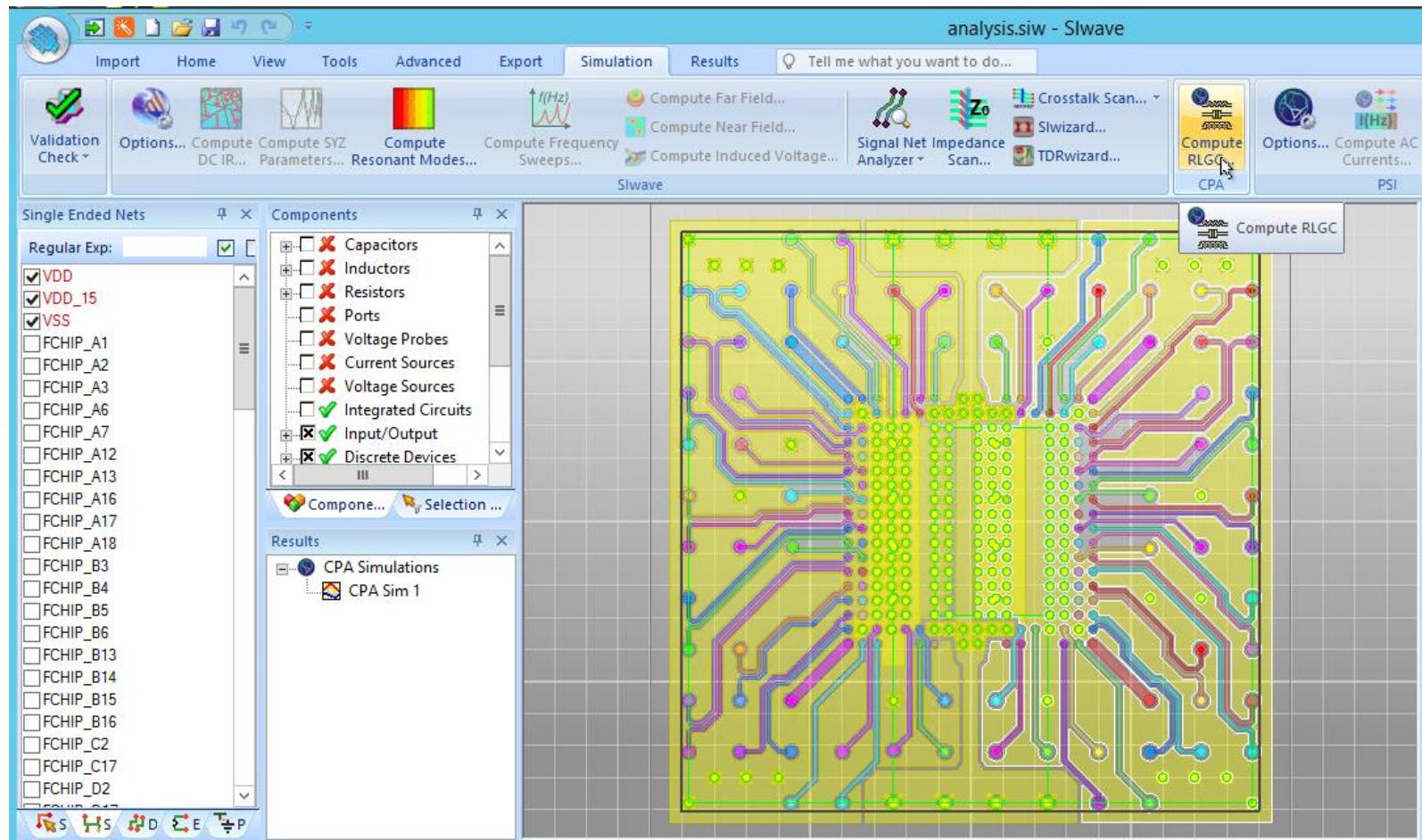

# General Setup and Usage

# SIwave-CPA

# Setup

**Note: Q3D solver extracts the whole geometry without any partitioning of structure.**

# Solver Selection Recommendation

## FEM Solver

No limit on number of sources and sinks

Packages and PCBs with well defined ground planes

Large scale PDN structures

RDL, Silicon Interposers, TSVs

No limit on number of Signal lines

## MoM Q3D Solver

Limited number of sources and sinks

Leadframe designs

Wirebond packages

Smaller flip-chip designs

SI analysis with “fewer” lines

Can handle larger designs – based on memory/run time requirements

*Note: We use FEM solver by default, unless Q3D solver is selected.*

*Note: Do not compare partial RLCG data between FEM and MoM solvers. They use different global reference. We can only compare Loop-RLCG results across solvers.*

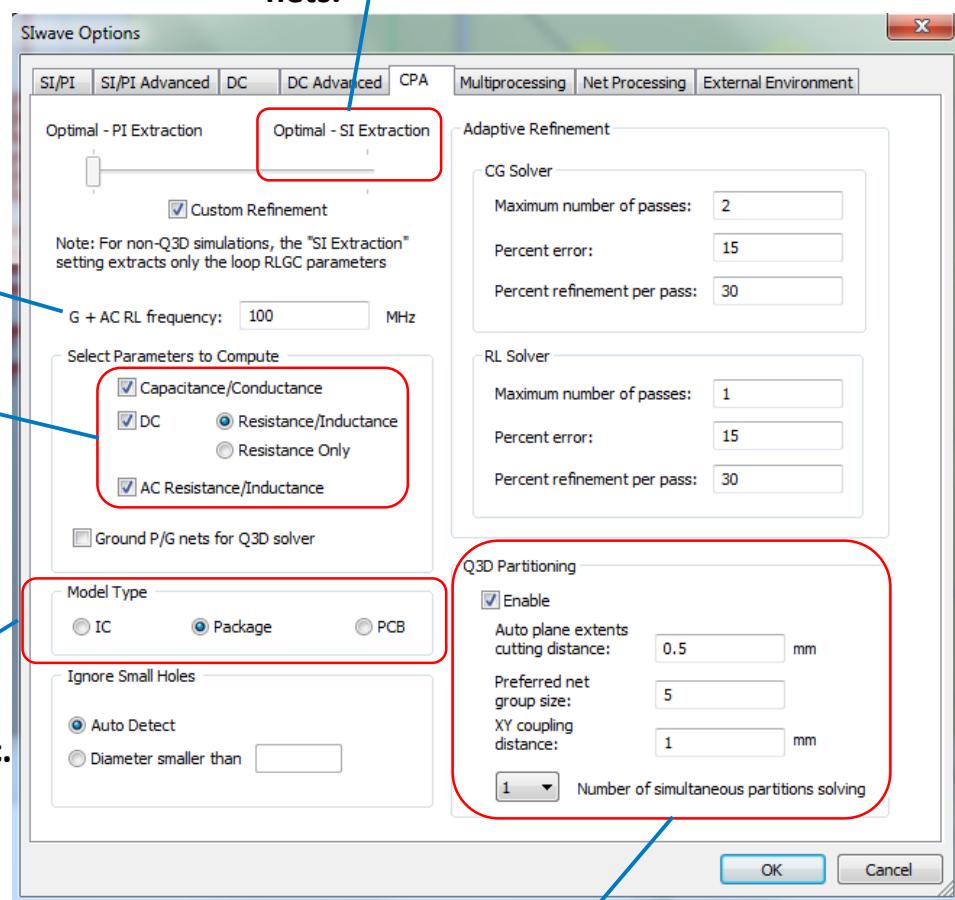

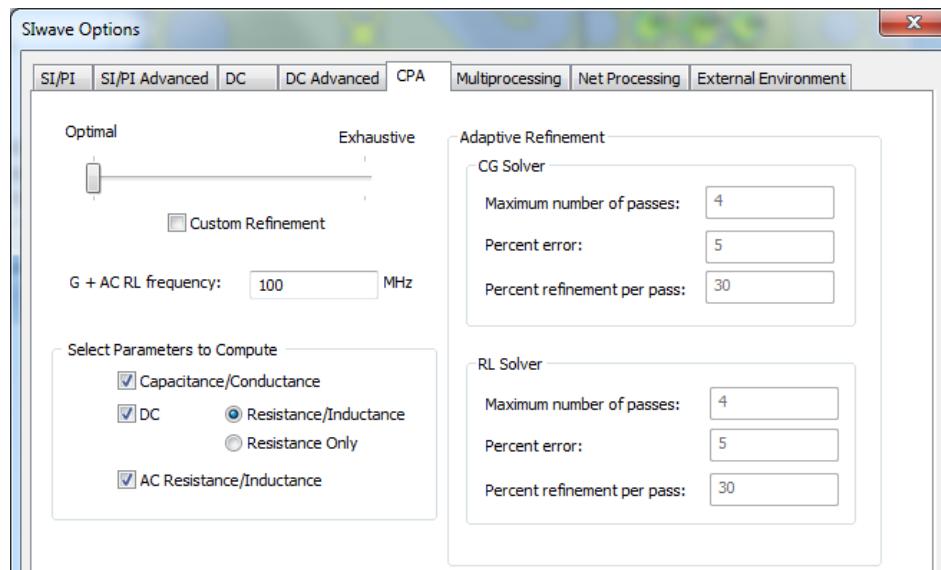

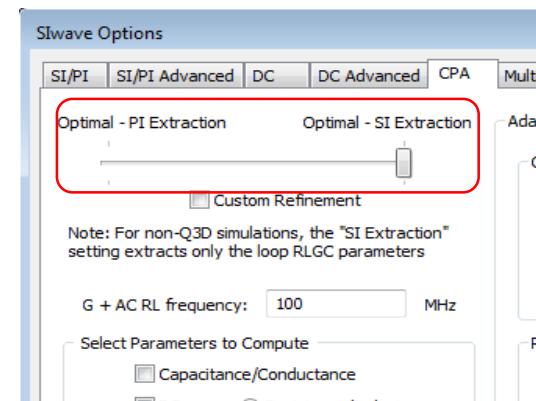

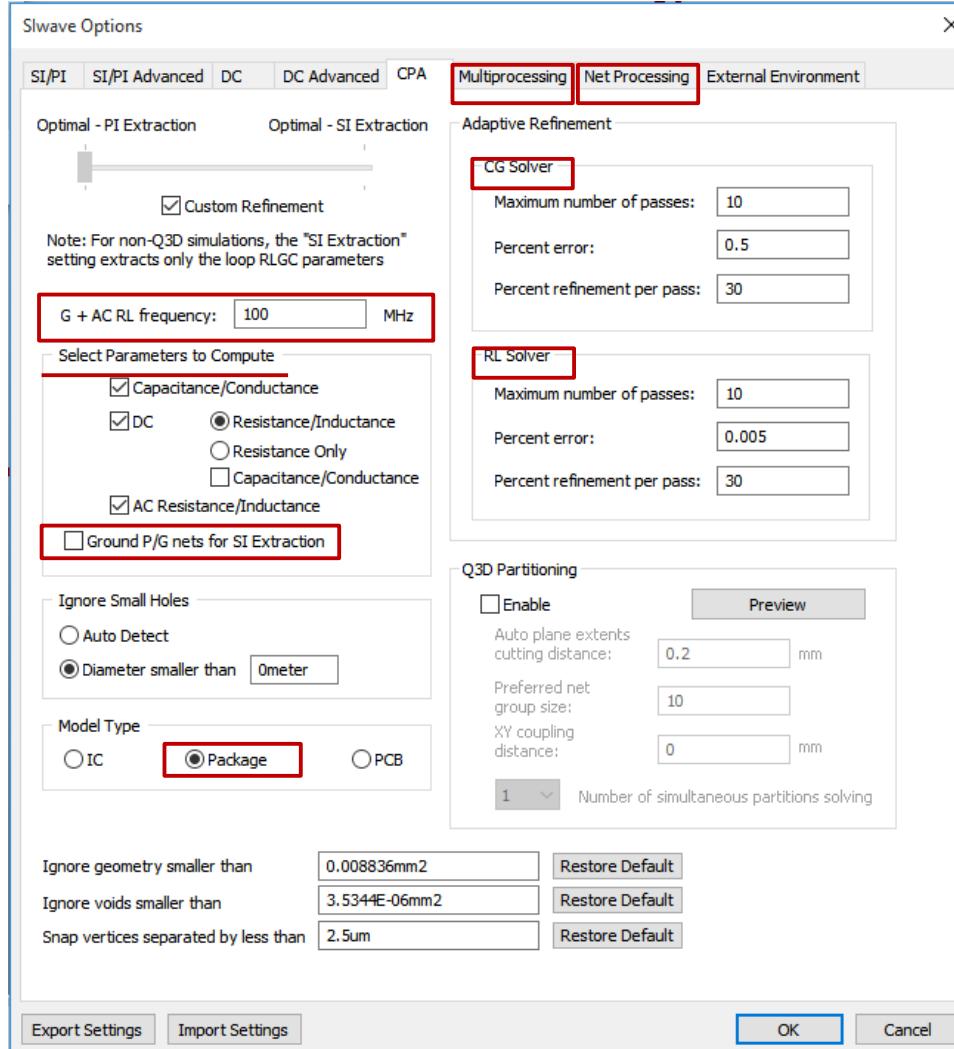

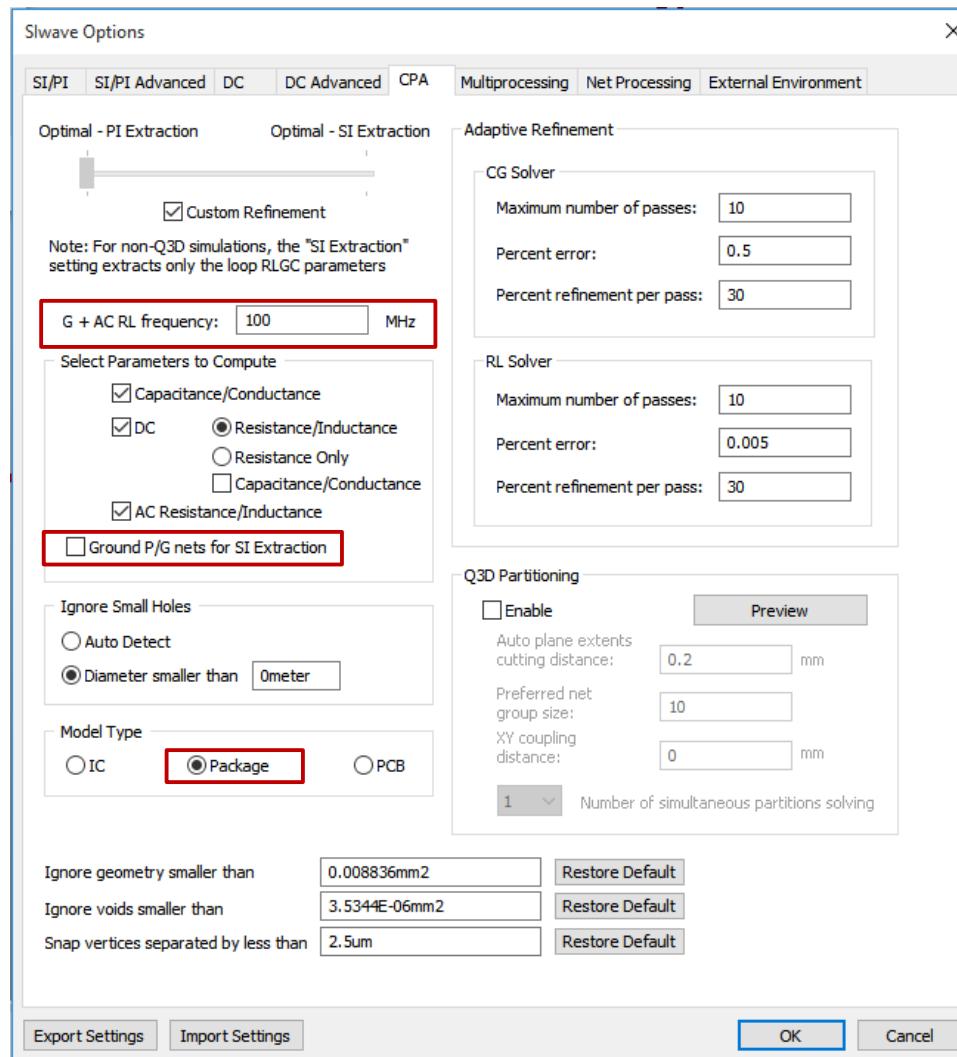

# CPA Options

**FEM solver:** Must be before 1<sup>st</sup> resonance. Typically, 100MHz for packages, and in KHz for PCBs.

**Q3D:** High enough for skin-effect to manifest.

Select both DC RL and AC RL together

**IC:** for RDL, interposer, etc.

**Package:** for wirebond, flip-chip, etc.

**PCB:** use for PCBs

**PKG+PCB:** Select Pacakage type

- Refer to HELP.

- Recommended only for SI extraction with large number of signal nets.

- Recommend to select Ground P/G nets for Q3D solver option.

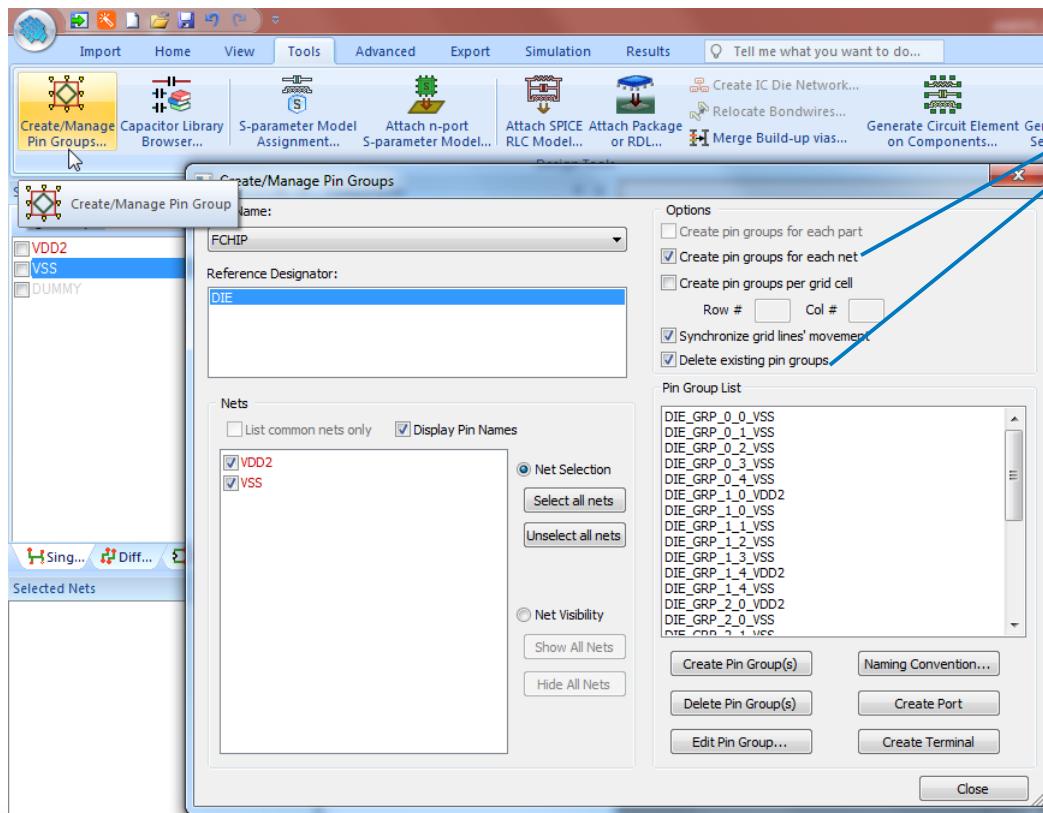

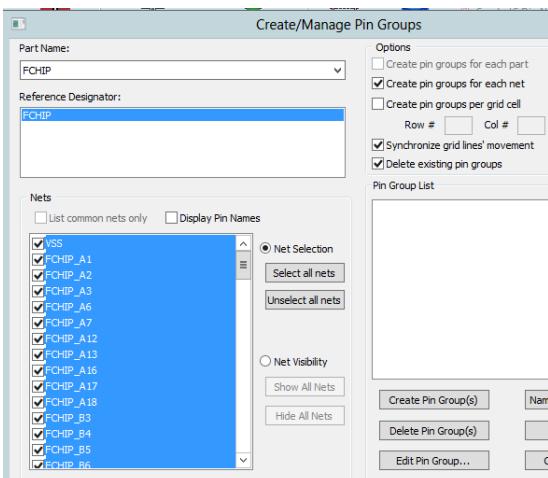

# Importance of Pin Groups

- Extraction is controlled by user-defined pin groups defined in the project.

- If RedHawk PLOC (or CPM) file is imported into Slwave, it also creates pin groups and these are subsequently used for extraction.

- Sources and Sinks can be defined on the pin groups.

Make sure to check these boxes while creating pin groups. Otherwise, pin groups would be created across nets, and there could be duplicates – Not supported for extraction.

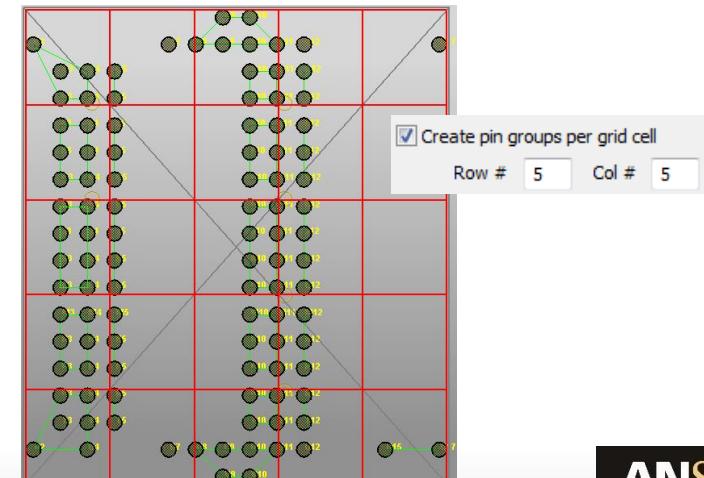

Pin groups can also be created on rectangular cells for the selected reference designator.

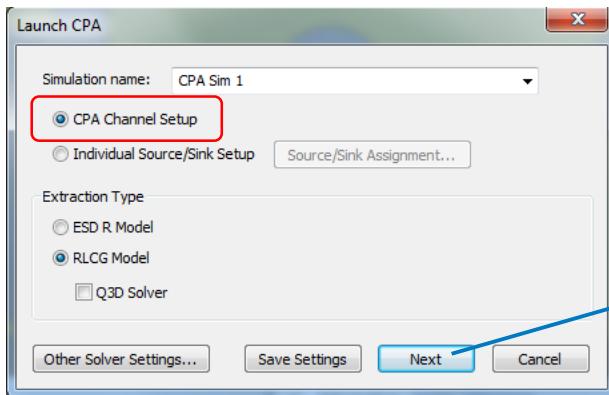

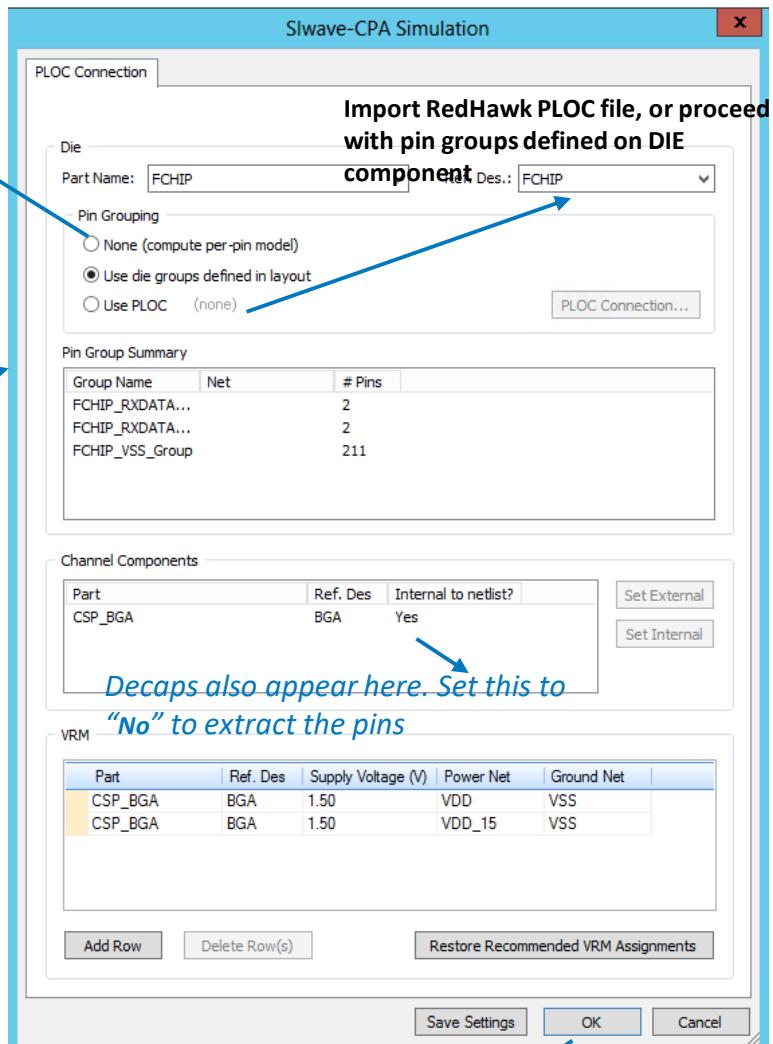

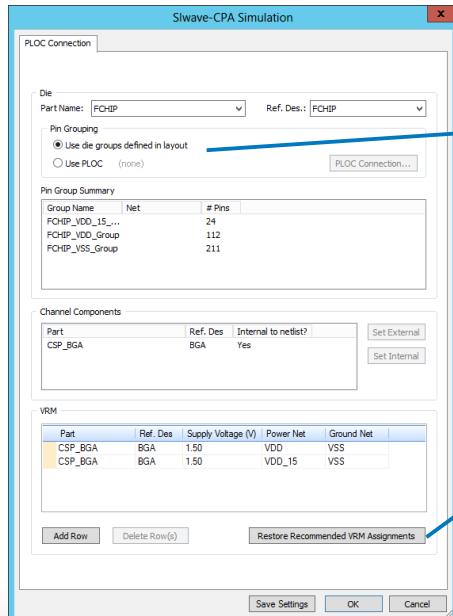

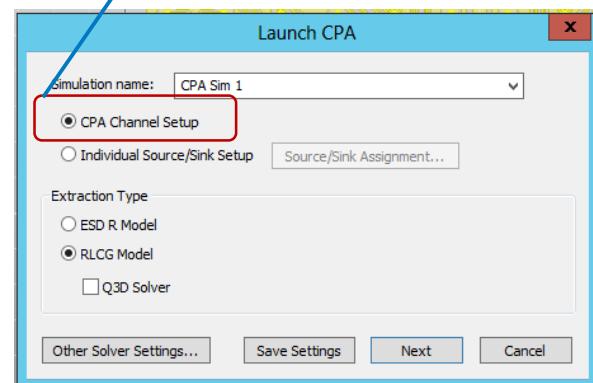

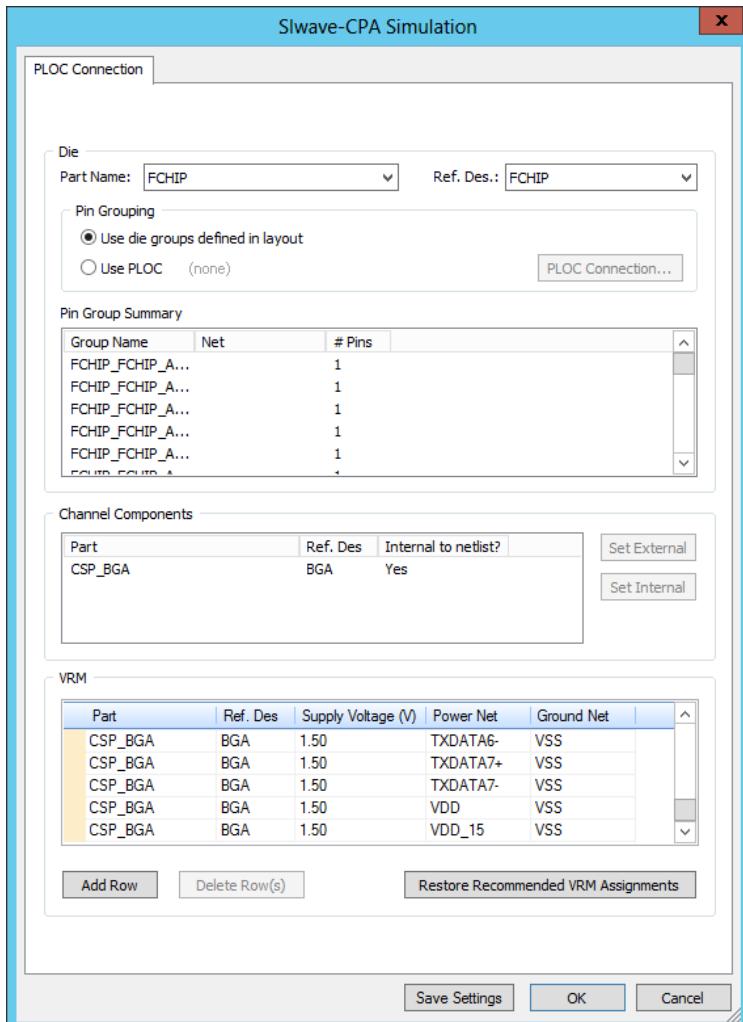

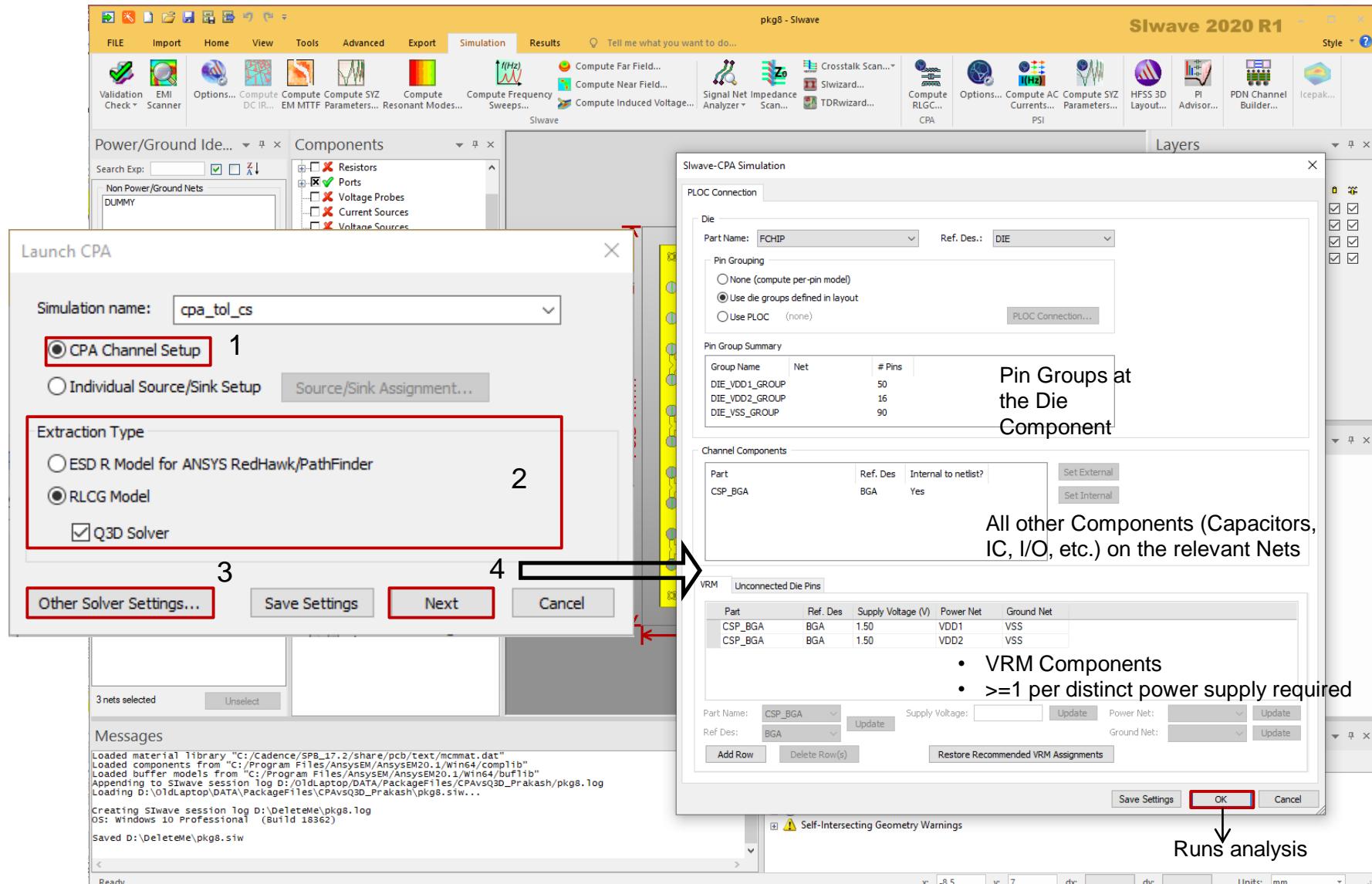

# CPA Channel Setup

Extract each pin

Majority of the structures have two or more components to be extracted. Without loss of generality, let us call them DIE, VRM and PDN components.

- Select a component as the DIE component – all of its pins become sources.

- Select a component as the VRM component – all of its pins become sinks.

- Any other components (second die, decaps, etc) are left as Channel components. Set their “Internal to netlist” flag to NO, if they also need to be extracted.

- Specify a supply voltage (leave as 1.5V, if not known). It has no impact on RLCK parasitics, and is only used by Chip level simulations.

**CPA Channel Setup must be used if the model is going to be used in RedHawk for system level simulations.**

**ANSYS**

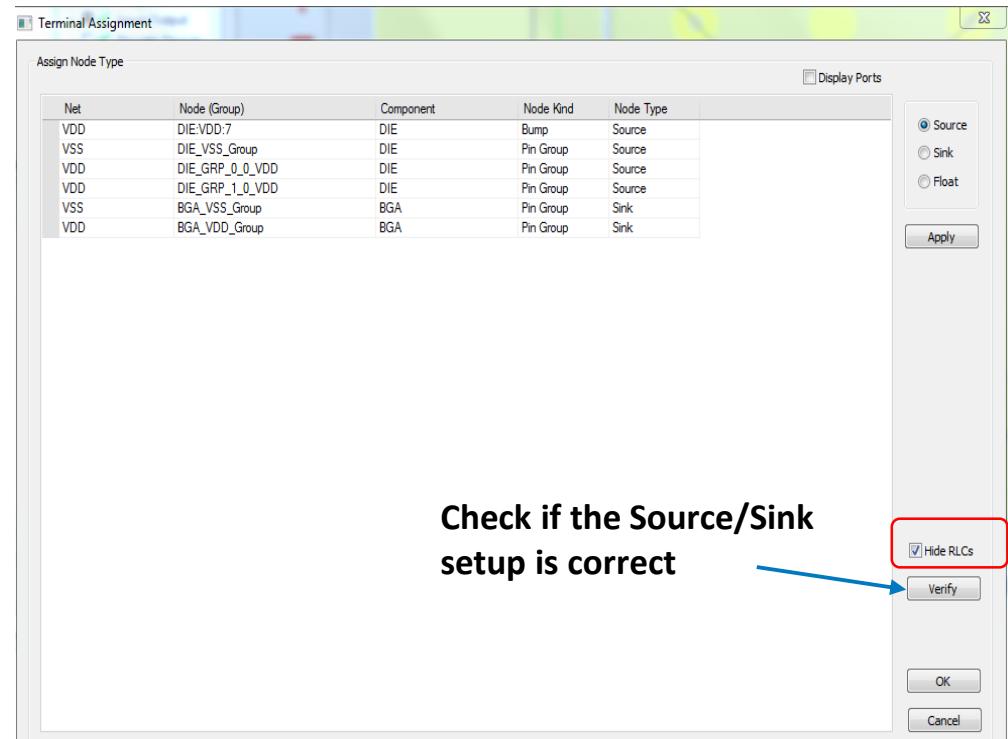

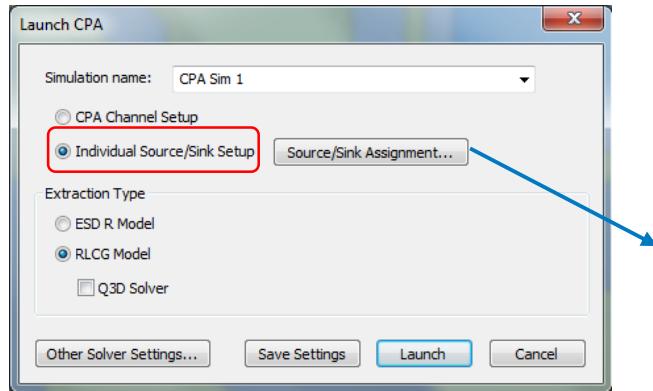

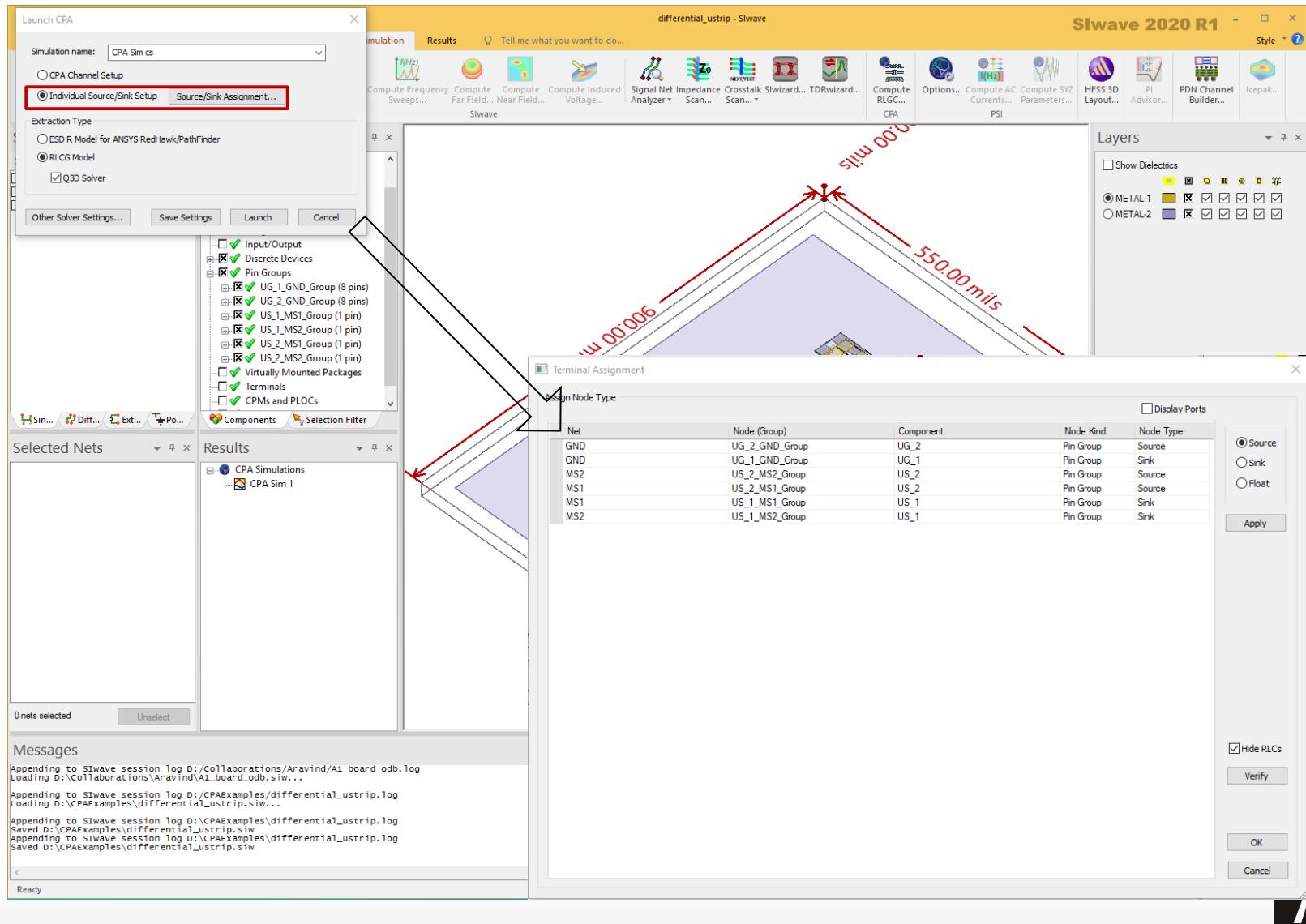

# Individual Source/Sink Setup

- Provides more flexible setup when needed.

- Pin groups and ungrouped pins appear in the table.

- Individual pins (groups) can be floated.

- Select multiple rows and set them as source, sink or float types.

- **Note that each net can only have one sink.**

- A pin group can only contain pins of same net.

- RedHawk PLOC hook-up and encrypted netlist generation not supported.

- RLCG extraction at the user-defined sources and sinks is performed.

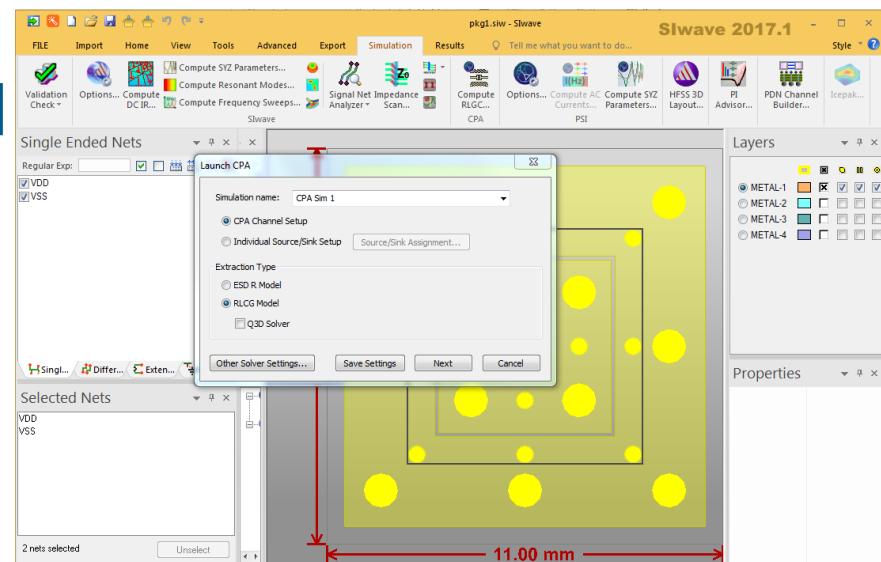

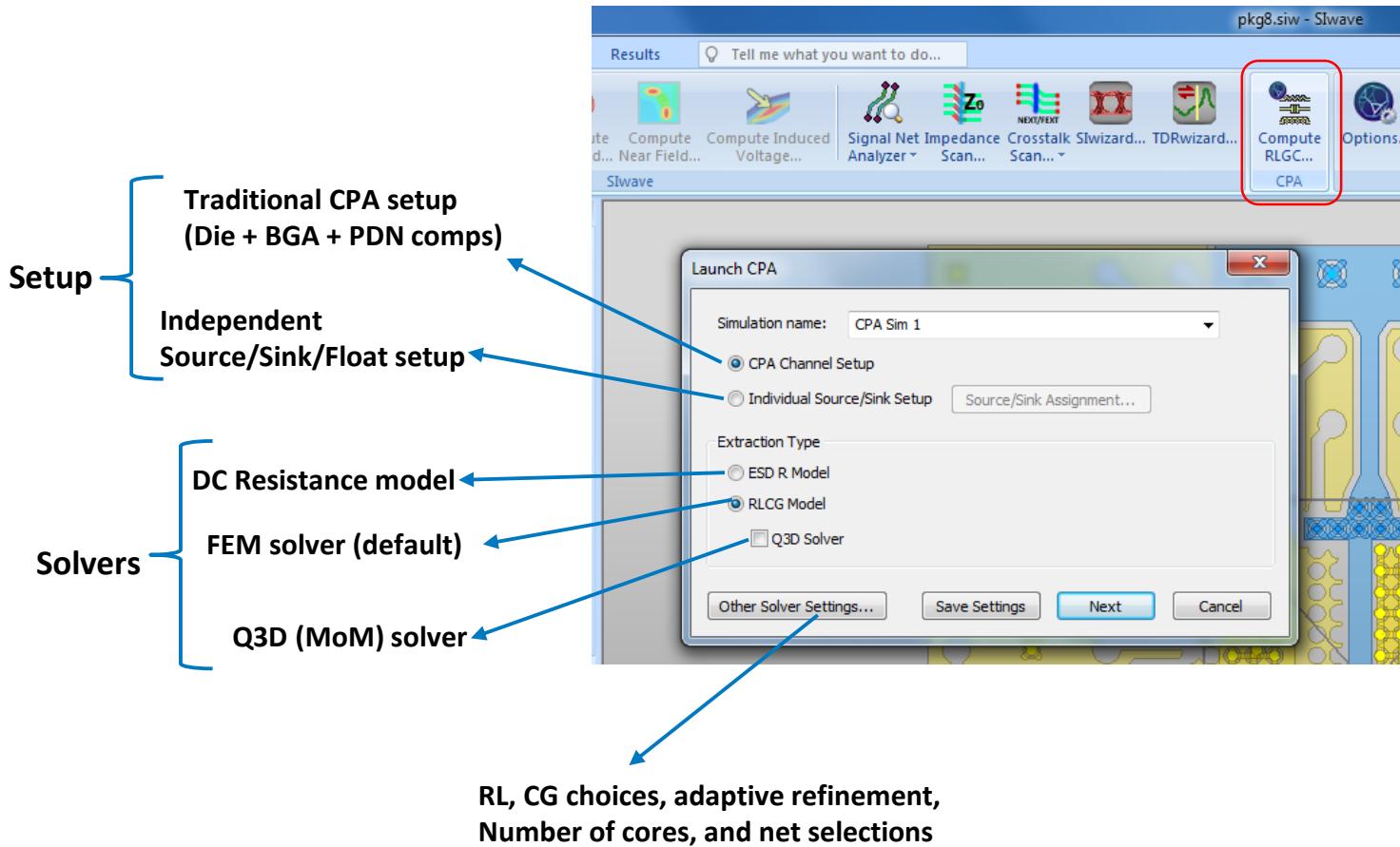

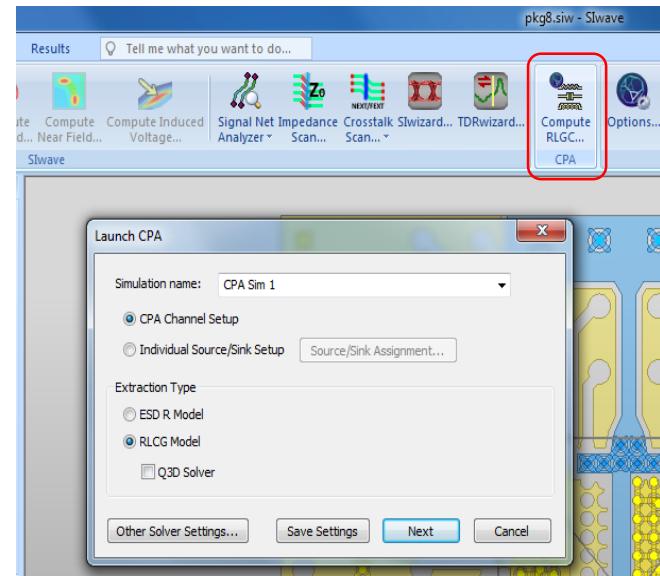

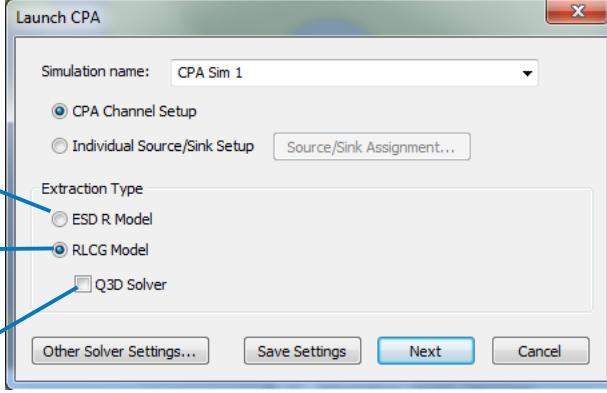

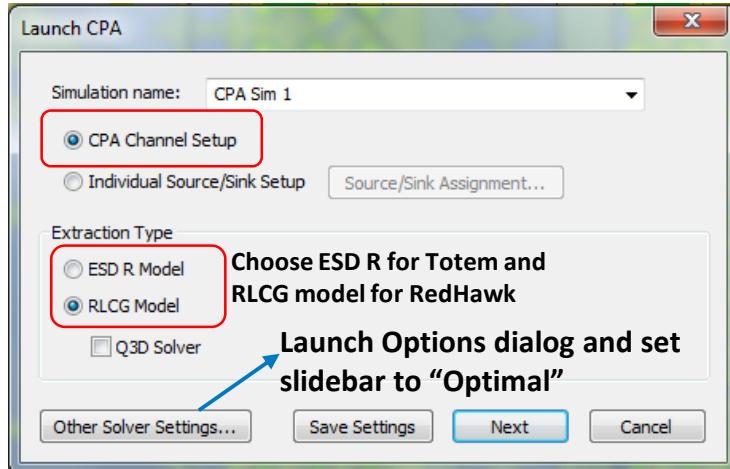

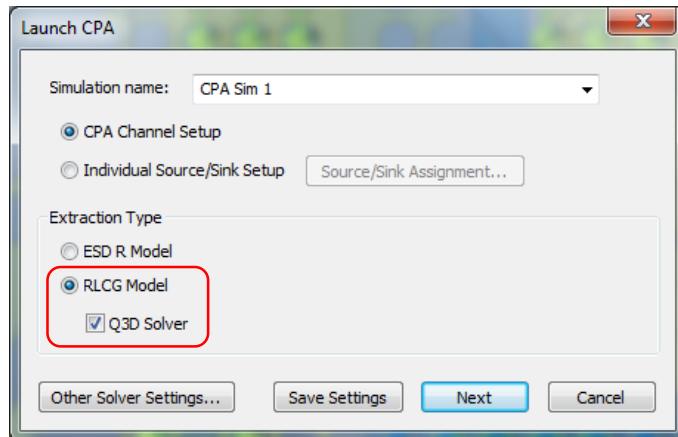

# Extraction Type (Solver choice)

Pure DC resistance extraction with the Spice netlist customized for Chip ESD applications

- Uses FEM solver.

- High capacity and fast turn-around time.

- Recommended for large PDN structures and (or) having several hundreds of source terminals.

- Recommended for IBIS modeling

▪ Uses Q3D MoM solver with adaptive meshing.

▪ Recommended for high accuracy applications.

▪ Ideal for leadframes, small scale packages, etc.

**Note:** ESD model always ungroups the pins on the BGA component, and extracts resistance for each and every pin. This is needed for chip-level ESD path tracing.

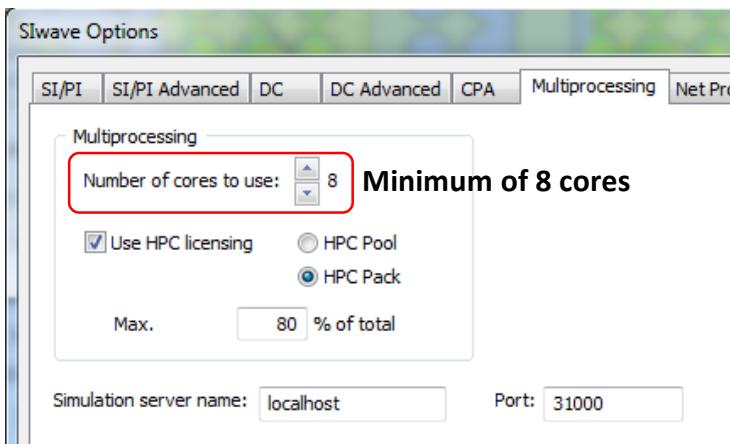

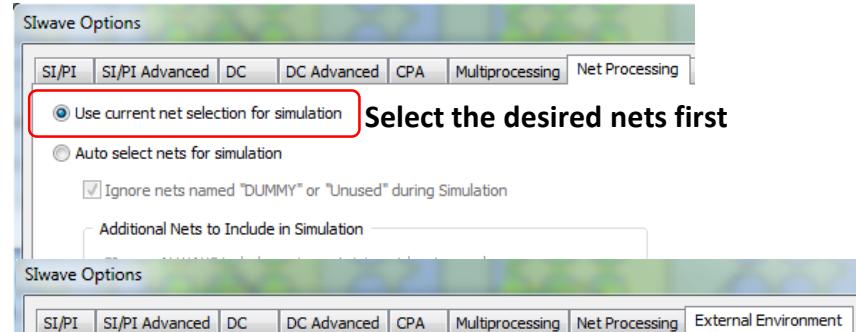

# Other Solver Settings

The image shows three overlapping dialog boxes from the ANSYS SIwave software. The top dialog is titled 'Launch CPA' and contains settings for a simulation named 'CPA Sim 1'. It includes options for 'CPA Channel Setup' (selected), 'Individual Source/Sink Setup', 'Extraction Type' (set to 'RLCG Model'), and a checkbox for 'Q3D Solver'. Below these are buttons for 'Other Solver Settings...', 'Save Settings', 'Next', and 'Cancel'. A blue arrow points from the 'Other Solver Settings...' button to the 'Multiprocessing' tab of the 'SIwave Options' dialog on the left. The middle dialog is also titled 'SIwave Options' and has the 'Multiprocessing' tab selected. It shows settings for 'Number of cores to use' (set to 8), 'Use HPC licensing' (checked), and 'Max. 80 % of total'. The bottom dialog is also titled 'SIwave Options' and has the 'Net Processing' tab selected. It includes options for 'User current net selection for simulation' (selected), 'Auto select nets for simulation', and a list of 'Additional Nets to Include in Simulation' with 'DUMMY' selected. A blue arrow points from the 'User current net selection for simulation' checkbox to the 'Additional Nets to Include in Simulation' list.

**Number of cores

(atleast 8 cores recommended)**

**Recommended to select desired nets, and check "User current net selection for simulation"**

Controls extraction frequency, DC/AC RL and CG setup

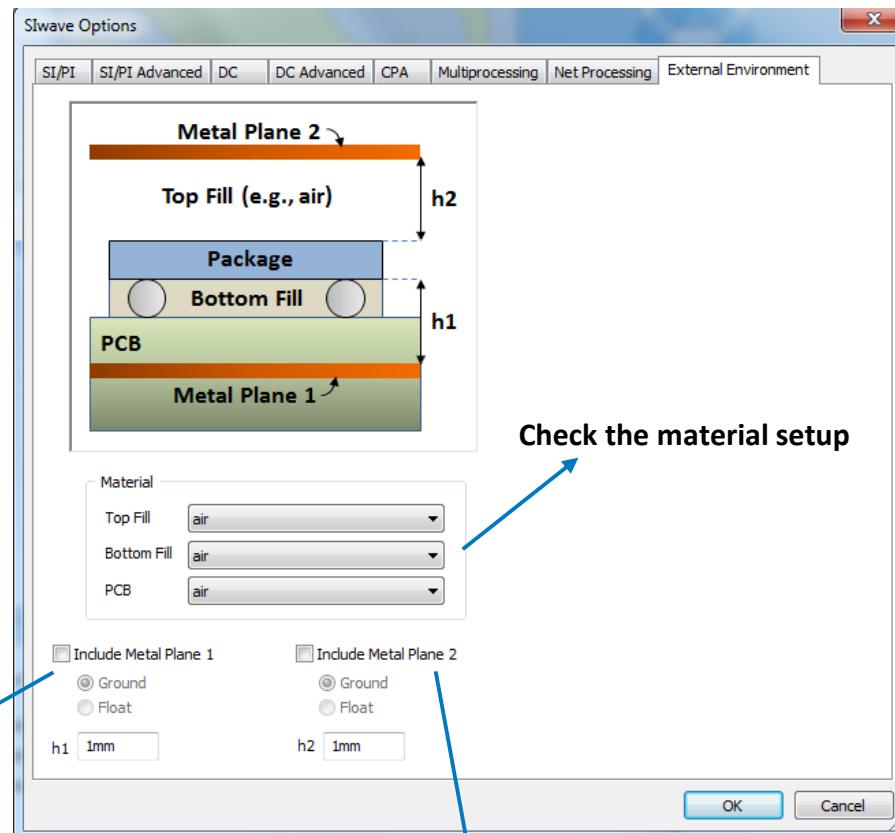

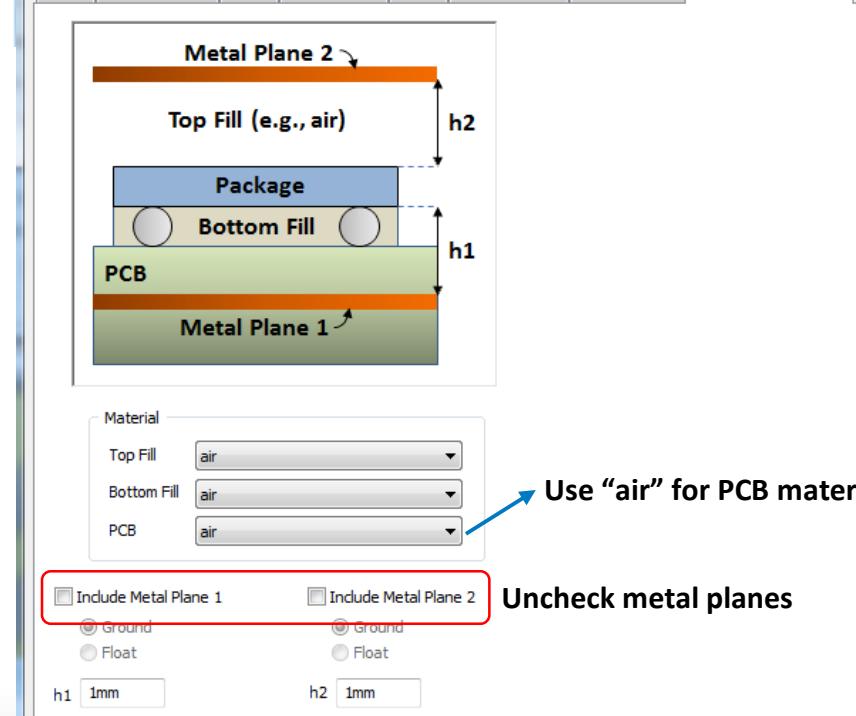

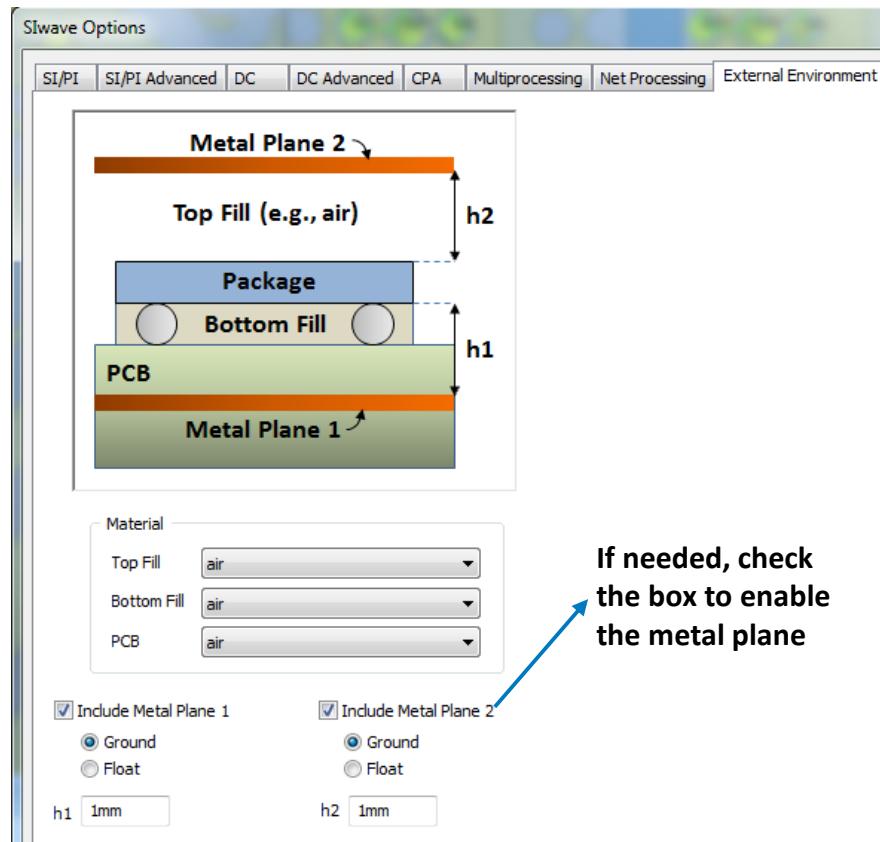

# Other Solver Settings – External Environment

**External Metal planes:**

Applicable only for Q3D MoM

Solver

- Check the box to add a metal plane (Ground or Float) under the geometry at  $h1$  distance.

- Note that “ $h1$ ” is measured from the bottom of the layer stackup, not counting solder balls if present.

- Check the box to add a metal plane (Ground or Float) above the geometry at  $h2$  distance.

- Note that “ $h2$ ” is measured from the top of the layer stackup, not counting solder bumps if present.

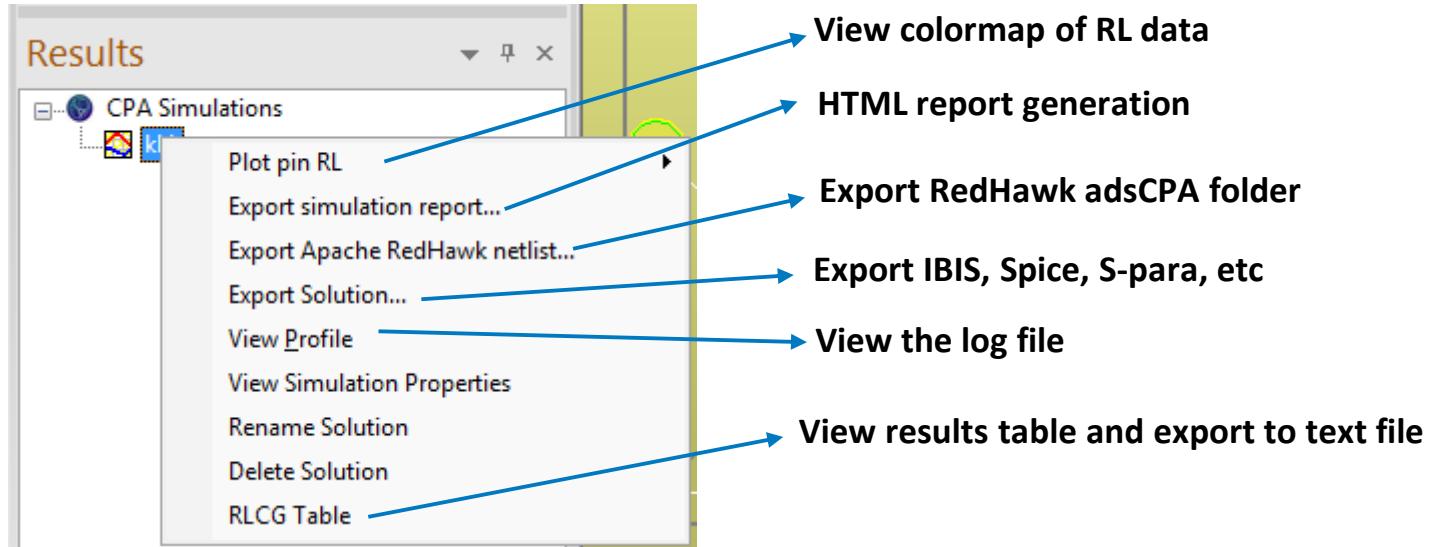

# Description of Extraction Results

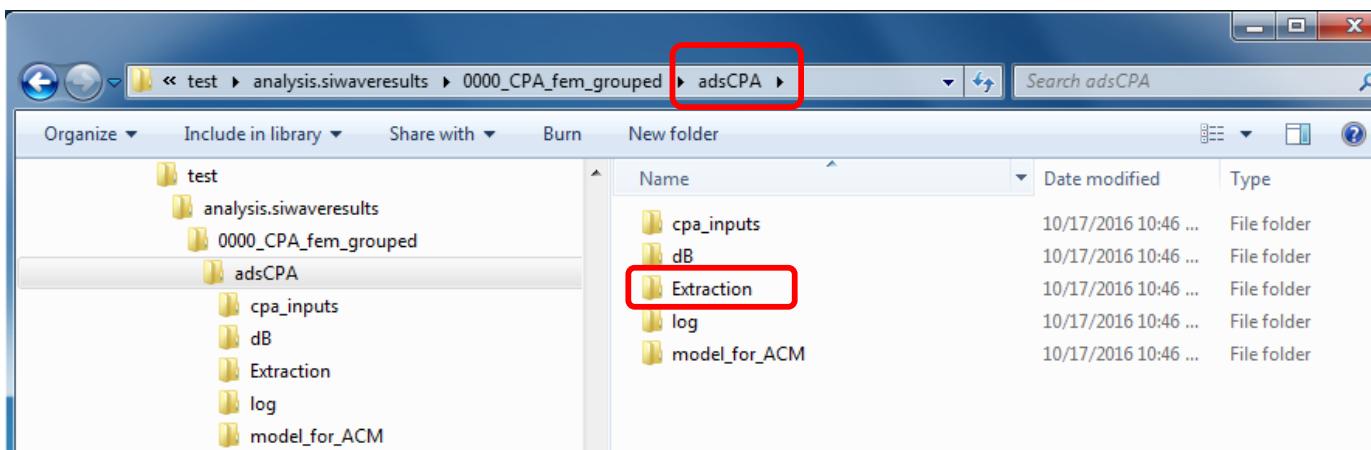

## Results Folder Structure

# Contents of *adsCPA/Extraction* folder

| Name                                 | Date modified        | Type          |

|--------------------------------------|----------------------|---------------|

| bin                                  | 10/17/2016 10:46 ... | File folder   |

| 0000_CPA_fem_grouped_CSP_BGA_BGA.cpp | 10/17/2016 10:46 ... | C++ Source    |

| 0000_CPA_fem_grouped_FCHIP_FCHIP.cpp | 10/17/2016 10:46 ... | C++ Source    |

| mult_whole.lvl                       | 10/17/2016 10:46 ... | LVL File      |

| mult_whole_dcres.lvl                 | 10/17/2016 10:46 ... | LVL File      |

| 0000_CPA_fem_grouped.pkg             | 10/17/2016 10:46 ... | PKG File      |

| cpa_annotated.ploc                   | 10/17/2016 10:46 ... | PLOC File     |

| cpa_annotated_ASCII.ploc             | 10/17/2016 10:46 ... | PLOC File     |

| 0000_CPA_fem_grouped.sp              | 10/17/2016 10:46 ... | SP File       |

| 0000_CPA_fem_grouped_CSP_BGA_BGA.sp  | 10/17/2016 10:46 ... | SP File       |

| cpa_rh_pkg_wrapper.sp                | 10/17/2016 10:46 ... | SP File       |

| cpa_rh_pkg_wrapper_ASCII.sp          | 10/17/2016 10:46 ... | SP File       |

| spiceModel_WT.sp                     | 10/17/2016 10:46 ... | SP File       |

| Cmatrix.txt                          | 10/17/2016 10:46 ... | Text Document |

| Gmatrix.txt                          | 10/17/2016 10:46 ... | Text Document |

| Loop_L.txt                           | 10/17/2016 10:46 ... | Text Document |

| Lumped_L.txt                         | 10/17/2016 10:46 ... | Text Document |

| Lumped_PerNet_R.txt                  | 10/17/2016 10:46 ... | Text Document |

| Partial_L.txt                        | 10/17/2016 10:46 ... | Text Document |

| Partial_L_VDD.txt                    | 10/17/2016 10:46 ... | Text Document |

| Partial_L_VDD_15.txt                 | 10/17/2016 10:46 ... | Text Document |

| Partial_L_VSS.txt                    | 10/17/2016 10:46 ... | Text Document |

| RLCG_Consolidated.txt                | 10/17/2016 10:46 ... | Text Document |

| Statistics.txt                       | 10/17/2016 10:46 ... | Text Document |

AC RLCG matrices

DC RL matrices

Empty BGA Spice deck (edit to add PCB models)

Encrypted wrapper for RedHawk/Totem

Top-level netlist for CPA model

For each net, we group all the DIE and VRM pins – compute the lumped resistance for each net (from die to VRM).

This is the partial L of each pin from DIE to VRM.

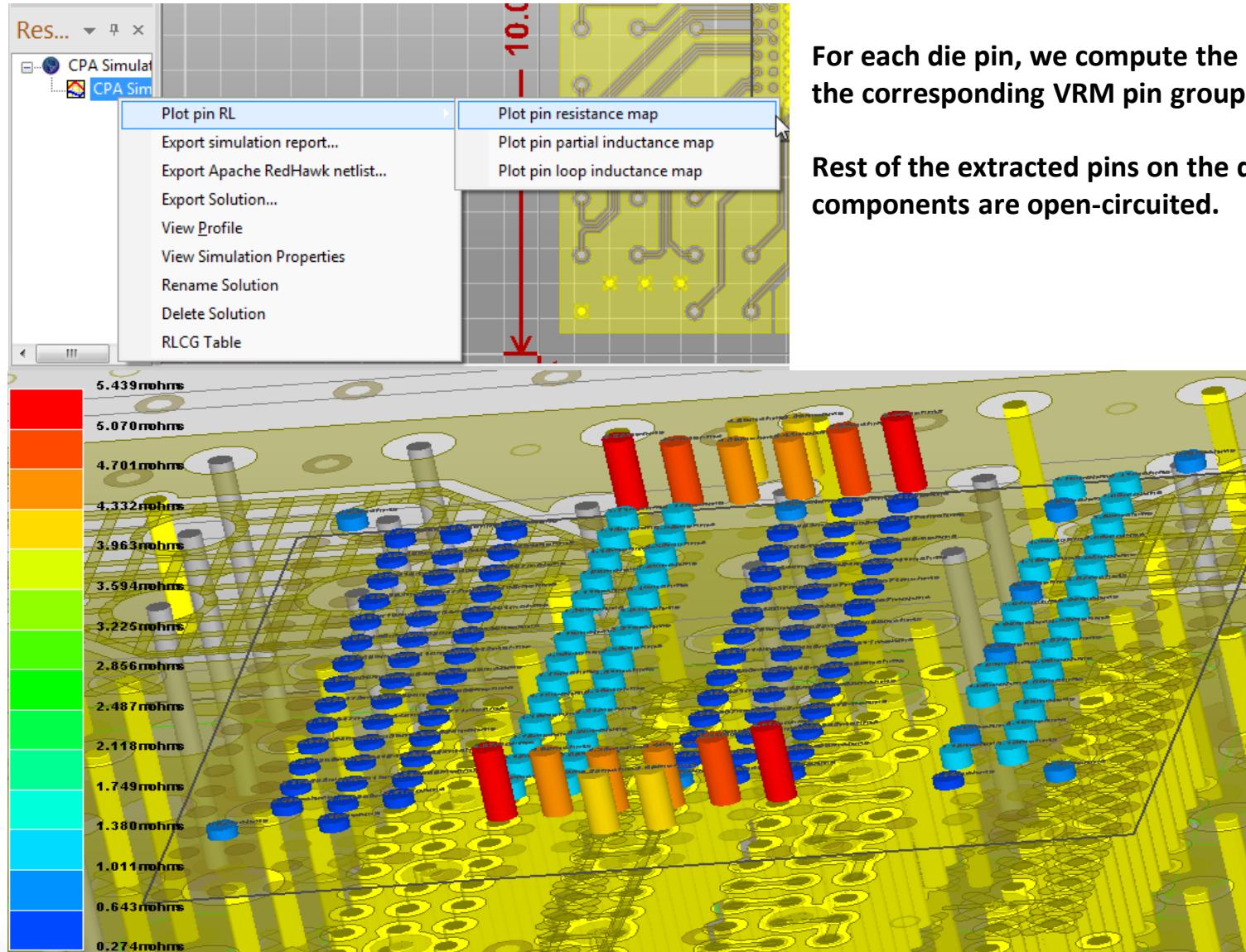

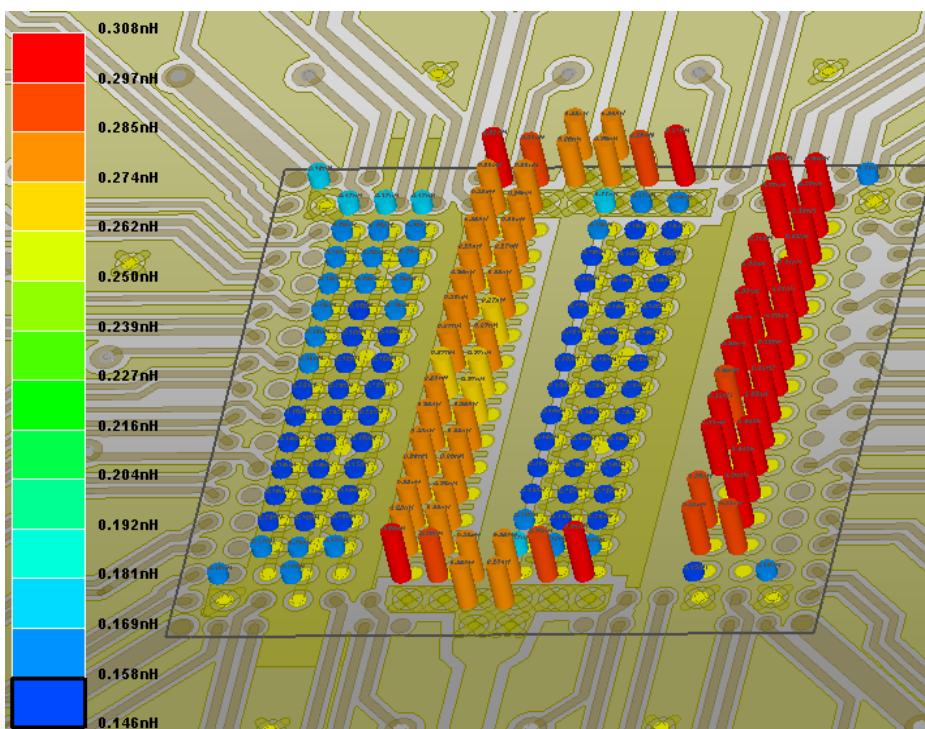

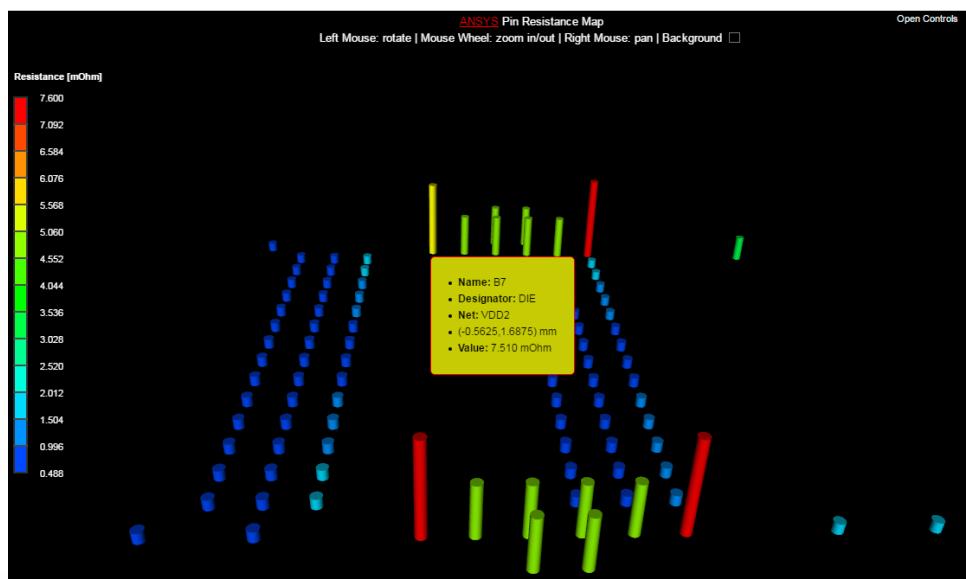

# Description of Extraction Results: Pin Resistance Map

# Description of Extraction Results: Pin Inductance Map

For each die pin, we compute the effective inductance to the corresponding VRM pin group of its net. This is the **partial branch inductance**.

Rest of the extracted pins on the die, vrm, and pdn components are open-circuited.

While the partial inductance per-pin is a useful feature, it is not a direct indicator of how well that pin behaves in the presence of chip.

That requires the computation of **Loop inductance** – as each pin can take the surrounding pins as return paths.

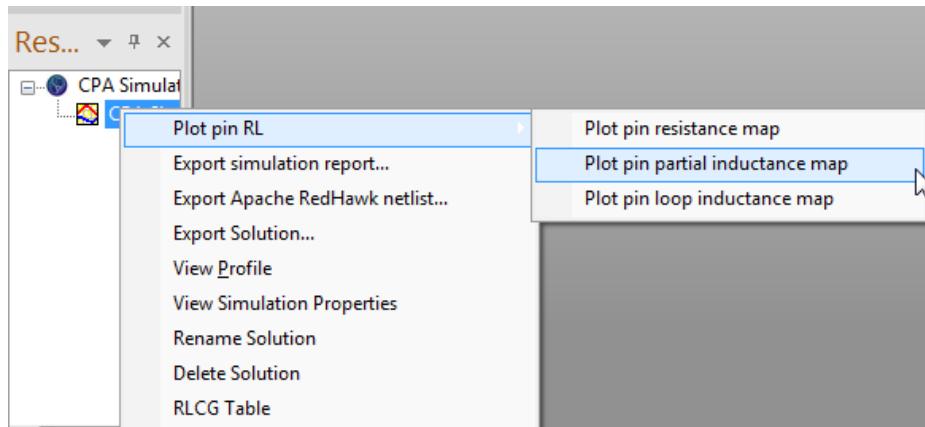

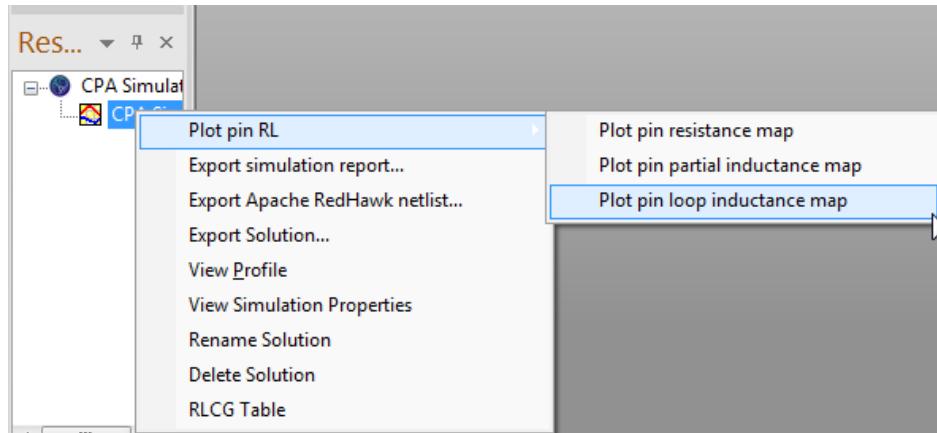

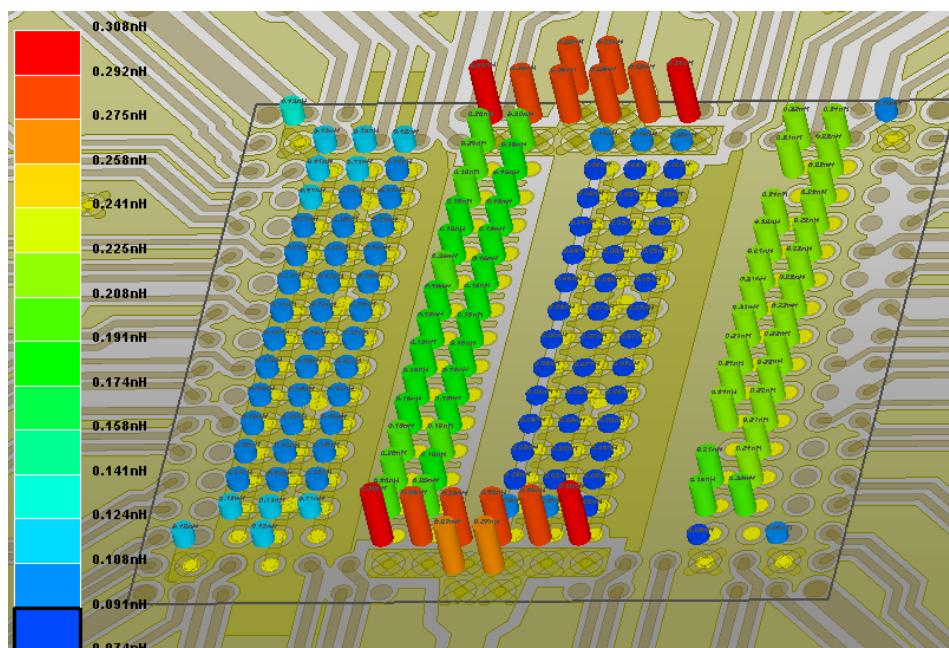

# Description of Extraction Results: Loop Inductance Map

Loop inductance is a post-processed result derived from the partial inductance matrix.

$$(L_{loop} = L_{11} - 2*L_{12} + L_{22})$$

Partial inductance matrix is what is used in the Spice netlist exported for RedHawk usage.

Loop inductance is presented to only aid user in troubleshooting the package design.

For each DIE power pin, we use all of the DIE ground pins as return paths and compute the Loop-L for the power pin.

Similarly, for each ground pin, we use all the DIE power pins as return paths.

Changes in Loop-L from one pin to another can be used to locate poorly routed pins.

# Loop Inductance Map (contd ...)

VDD and VDD\_15 pins use VSS as return path

VSS pins use both VDD and VDD\_15 as return paths

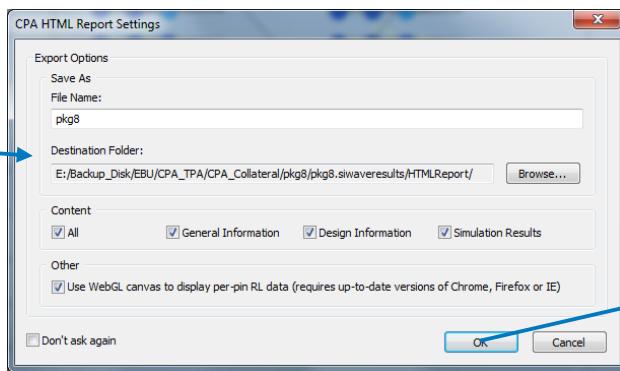

# Description of Extraction Results

## HTML Report

### Siwave CPA Simulation Report

#### Table of Contents

- 1 General Information

- 2 Design Information

- 2.1 Layer Stackup

- 2.2 Materials

- 2.3 Layer View

- 2.4 Solder Bumps/Balls

- 3 Simulation Results

- 3.1 RL Statistics per domain

- 3.2 Per-domain Histograms

- 3.3 Pin RL data for all nets

- 3.4 Pin RL color map

- 3.5 Pin RL data for Net = VDD2

- 3.6 Pin RL data for Net = VSS

- 3.7 Lumped Resistance and Partial Inductance matrix

- 3.8 Per-domain Capacitance matrix

## Interactive 3D Display of RL data in the HTML Report

# SIwave CPA Simulation Report

## Table of Contents

---

### [1 General Information](#)

### [2 Design Information](#)

#### [2.1 Layer Stackup](#)

#### [2.2 Materials](#)

#### [2.3 Layer View](#)

#### [2.4 Solder Bumps/Balls](#)

#### [2.5 External Environment](#)

#### [2.6 Nets Selected for Simulation](#)

### [3 Channel Information](#)

#### [3.1 Die](#)

#### [3.2 Channel Components](#)

#### [3.3 VRM](#)

### [4 Simulation Control](#)

#### [4.1 Multiprocessing Options](#)

#### [4.2 Net Processing Options](#)

#### [4.3 CPA Options](#)

### [5 Simulation Results](#)

#### [5.1 Ball, Bump and Via Statistics](#)

#### [5.2 RL Statistics per domain](#)

#### [5.3 Per-domain Histograms](#)

#### [5.4 Pin RL data for all nets](#)

#### [5.5 Pin RL color map](#)

**A comprehensive report of the layout, setup and the analysis of simulation results is presented in the HTML form.**

**Colormaps in the report are interactive in nature and can be modified within the report.**

**Histograms and 2D plots of the results are also presented.**

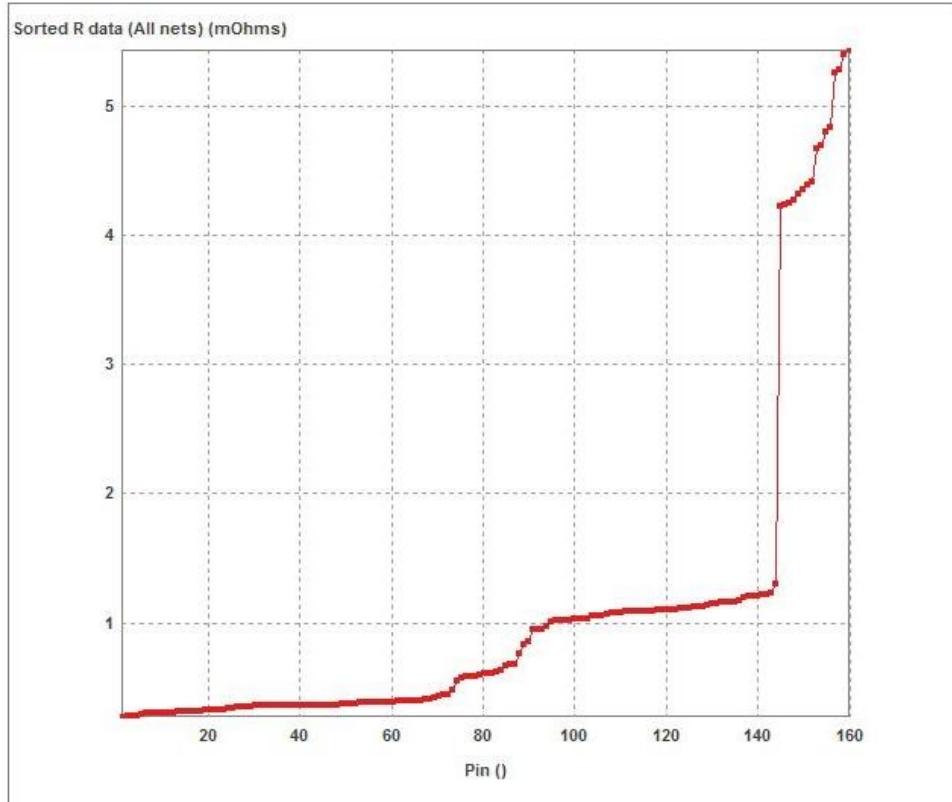

# HTML Report Description

Sorted R data (All nets)

**For each die pin the effective resistance is plotted.**

**The resistance is sorted from low to high so that identifying how pins are outliers would be easy.**

**Similarly, the sorted (low to high) data for inductance is also available.**

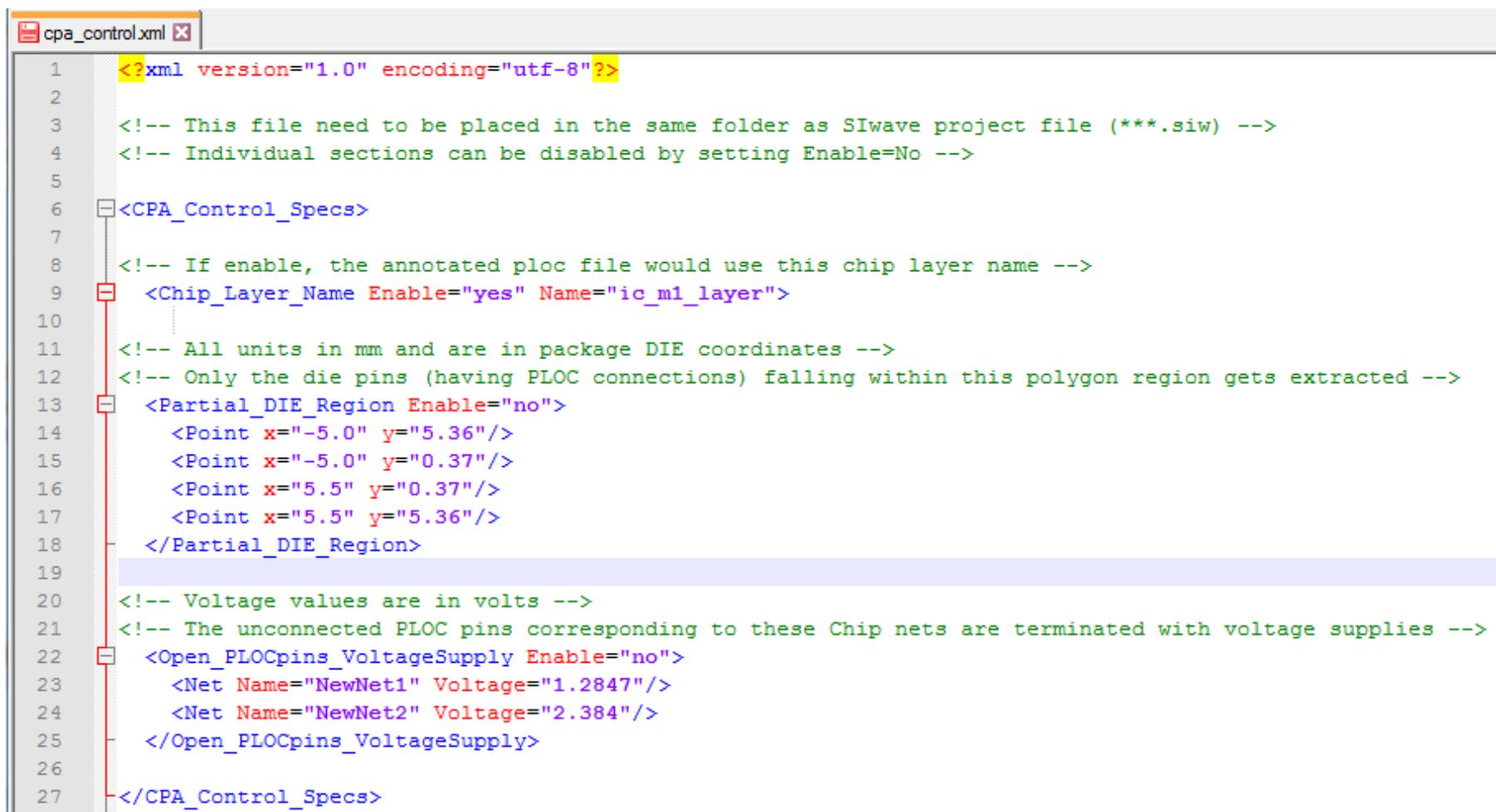

# cpa\_control.xml

User can edit this file to do certain things not yet available in the GUI.

Keep this file at the location of the .siw project file and run simulation.

```

1  <?xml version="1.0" encoding="utf-8"?>

2

3  <!-- This file need to be placed in the same folder as SIwave project file (***.siw) -->

4  <!-- Individual sections can be disabled by setting Enable=No -->

5

6  <CPA_Control_Specs>

7

8  <!-- If enable, the annotated ploc file would use this chip layer name -->

9  <Chip_Layer_Name Enable="yes" Name="ic_m1_layer">

10 <!-- All units in mm and are in package DIE coordinates -->

11 <!-- Only the die pins (having PLOC connections) falling within this polygon region gets extracted -->

12 <Partial_DIE_Region Enable="no">

13   <Point x="-5.0" y="5.36"/>

14   <Point x="-5.0" y="0.37"/>

15   <Point x="5.5" y="0.37"/>

16   <Point x="5.5" y="5.36"/>

17 </Partial_DIE_Region>

18

19 <!-- Voltage values are in volts -->

20 <!-- The unconnected PLOC pins corresponding to these Chip nets are terminated with voltage supplies -->

21 <Open_PLOCpins_VoltageSupply Enable="no">

22   <Net Name="NewNet1" Voltage="1.2847"/>

23   <Net Name="NewNet2" Voltage="2.384"/>

24 </Open_PLOCpins_VoltageSupply>

25

26 </CPA_Control_Specs>

27

```

# Application Specific Examples

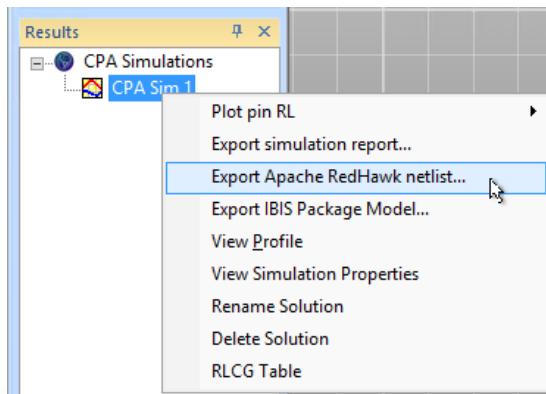

# Model Generation for ANSYS RedHawk and Totem

## Recommended Setup

# Model Generation for ANSYS RedHawk

Import PLOC (if available), or use existing pin groups.

Restore recommended settings, and then setup proper supply voltages.

## PDN System setup for RedHawk CPA model

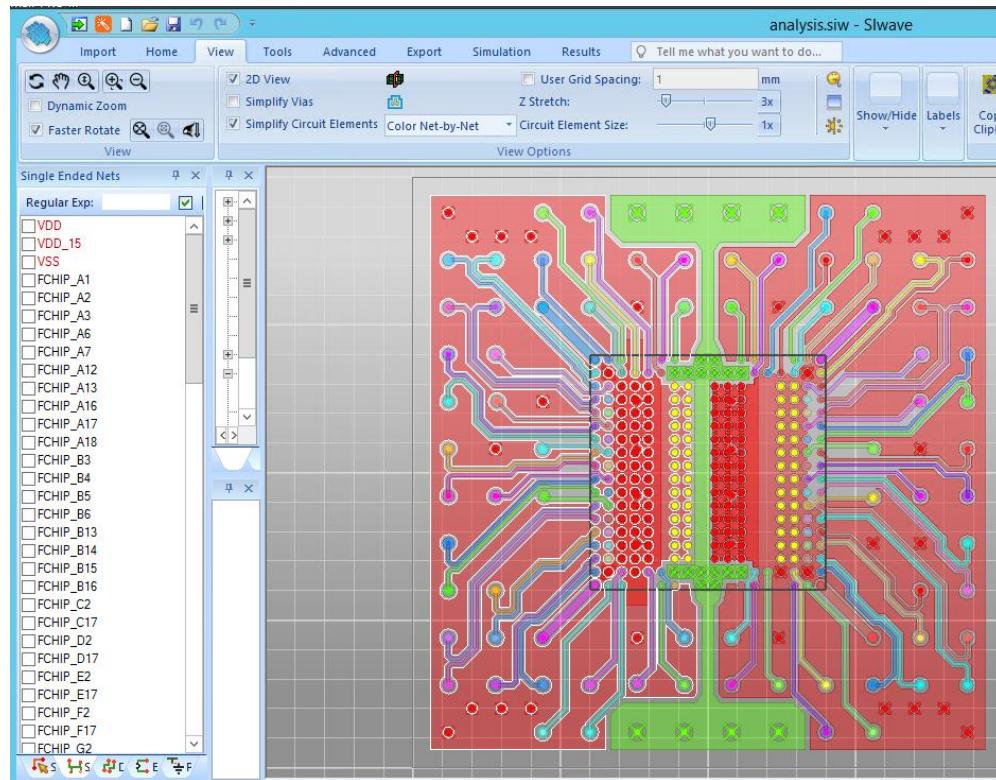

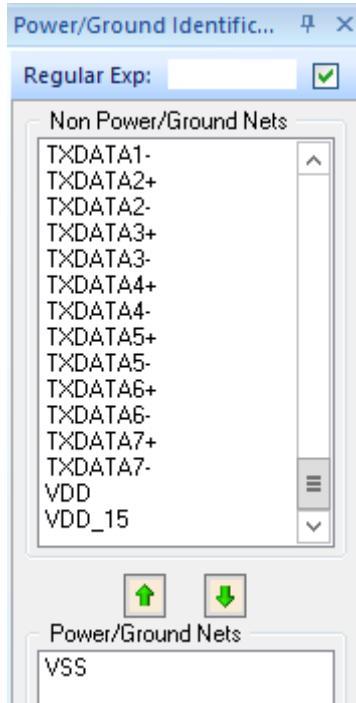

- Select VDD, VDD\_15 and VSS nets.

- Create pin groups on DIE and BGA components. Pin groups on DIE component can be skipped, if a PLOC file is available.

- Proceed with extraction.

- Export RedHawk netlist from the results.

# General RLCG Extraction

- Choose appropriate setup (Channel setup or Individual Src/Snk setup)

- Selecting RLCG Model enables high capacity FEM solver: ideal for PDN analysis of large structures and those requiring 100's to 1000's of terminals

- Choose Q3D solver for high accuracy application needs, which also allows independent extractions such as, DC RL only, AC RL only or just the CG extraction (or some combinations of those)

- Extraction frequency and adaptive refinement parameters can be custom set, or left at default.

- Recommendations for Multiprocessing, Net Processing and External Environment are same as before (atleast 8 cores, use current net selection, etc.)

# External Metal Planes

Some applications may require the presence of top and bottom metal planes.

- Each of the metal planes can be grounded (shorted – at internally generated terminals for inductance calculations).

- They can be floated (or open-circuited).

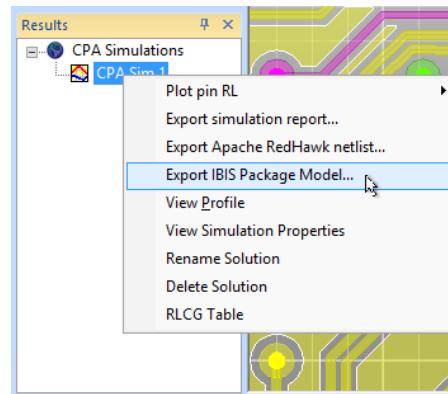

# Package IBIS Model Generation

**3 Power/Ground nets

All Signals on the package**

**Set dielectric fill to EDB\_FR-4**

| Color       | Name        | Type       | Thickness (microns) | Material   | Conductivity (S/m) | Dielectric Fill | Dielectric constant |

|-------------|-------------|------------|---------------------|------------|--------------------|-----------------|---------------------|

| Yellow      | TOP         | METAL      | 30.48               | EDB_COPPER | 5.959E+07          | EDB_AIR         | 1                   |

| Light Green | UNNAMED_002 | DIELECTRIC | 203.2               | EDB_FR-4   | 0                  | EDB_FR-4        | 4.5                 |

| Dark Blue   | VDD_C1      | METAL      | 30.48               | EDB_COPPER | 5.959E+07          | EDB_FR-4        | 4.5                 |

| Light Blue  | UNNAMED_004 | DIELECTRIC | 203.2               | EDB_FR-4   | 0                  | EDB_FR-4        | 4.5                 |

| Cyan        | VSS_C1      | METAL      | 30.48               | EDB_COPPER | 5.959E+07          | EDB_FR-4        | 4.5                 |

| Light Green | UNNAMED_006 | DIELECTRIC | 203.2               | EDB_FR-4   | 0                  | EDB_FR-4        | 4.5                 |

| Red         | BOTTOM      | METAL      | 30.48               | EDB_COPPER | 5.959E+07          | EDB_AIR         | 1                   |

# Package IBIS Model Generation

## Step-1

## Step-2

## Step-3

IBIS model not available for Individual Src/Snk setup

**Select “SI Extraction” option to get better accuracy for SI problems and also to compute loop-based RLCG data needed for IBIS.**

- 1) Net types do not matter. Nets can be set as Signal or PG types.

- 2) Group all the pins of each net on Die, and repeat on BGA.

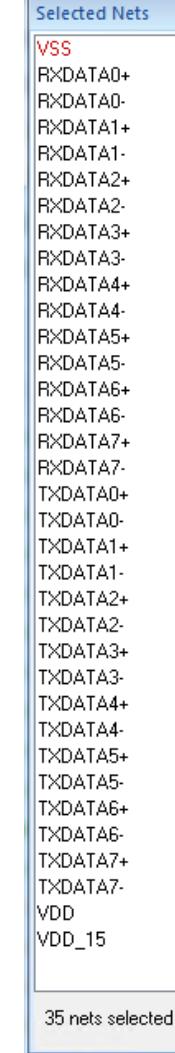

- 3) Select VDD, VDD\_15, VSS, and all DAT+ and DAT- nets.

- 4) Go to Other Solver settings and select “Exhaustive” from sidebar and from Net processing tab, choose “Use current net selection for simulation”.

# Package IBIS Model Generation

- 5) Set FCHIP as the Die component, and CSP\_BGA as VRM.

- 6) Start the simulation.

- 7) Once the simulation is done, RLCG table can be viewed, and the IBIS model can be exported.

```

0001_CPA_Sim_1.pkg

1 [IBIS Ver]      5.0

2 [Comment Char]  l_char

3 [File Name]    0001_CPA_Sim_1.pkg

4 [File Rev]     1.0

5 [Date]         Fri Aug 12 11:54:53 2016

6

7 [Source]

8 [Notes]

9 [Disclaimer]

10 [Copyright]

11

12 [Define Package Model] 0001_CPA_Sim_1

13 [Manufacturer] unknown

14 [OEM]          unknown

15 [Description]  unknown

16

17 [Number Of Pins] 35

18

19 [Pin Numbers]

20 | Pin Name Terminal      Net Name      Starting Node      Ending Node

21 | B18 | 1                 RXDATA0+  FCHIP_FCHIP_n237  CSP_BGA_BGA_n674

22 | C18 | 2                 RXDATA0-  FCHIP_FCHIP_n236  CSP_BGA_BGA_n673

23 | E18 | 3                 RXDATA1+  FCHIP_FCHIP_n232  CSP_BGA_BGA_n669

24 | D18 | 4                 RXDATA1-  FCHIP_FCHIP_n233  CSP_BGA_BGA_n670

```

**IBIS .pkg model**

# Key Setup Guidelines

- For simulation performance & accuracy, **classify various nets properly**

- Large planes as Power/Ground nets

- Signal Nets as Non-Power/Ground nets

- Define solderballs and solderbumps for appropriate padstacks

- Define Pin Groups as needed

- **SIwave** (see example projects for details)

- **Tools -> Sanitize Layout** to clean up planes and traces #1

- **Simulation -> Validation Check** to identify and fix any problem areas #2

- **Simulation -> Compute RLGC (CPA)** -> select either **Individual Source/Sink** or **CPA channel setup**,

- **Individual source/sink setup**-- user defines source/sink per pin or pin group

- **CPA Channel setup** – user specifies Die, Channel components, VRM

- Set **Extraction Type: RLGC Model** only -> **CPA** fast FEM; **Q3D Solver** -> MoM Solver

- Under **Other Solver Settings**, setup **Netprocessing**, **Multiprocessing**, **CPA** options

- **Run analysis & post-process** results

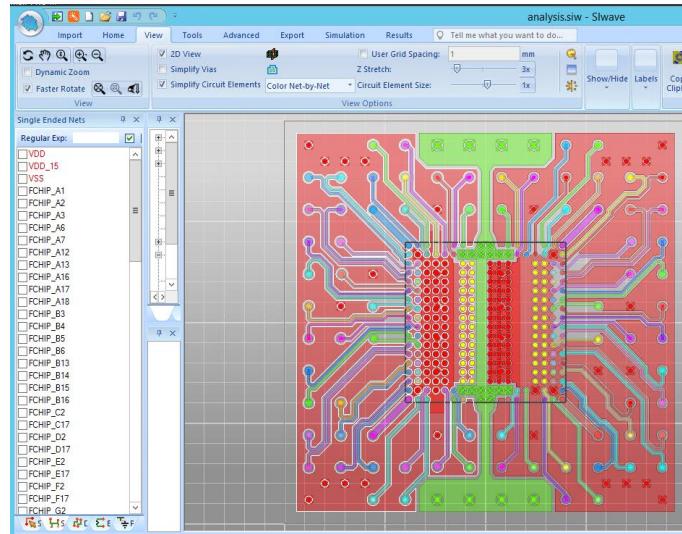

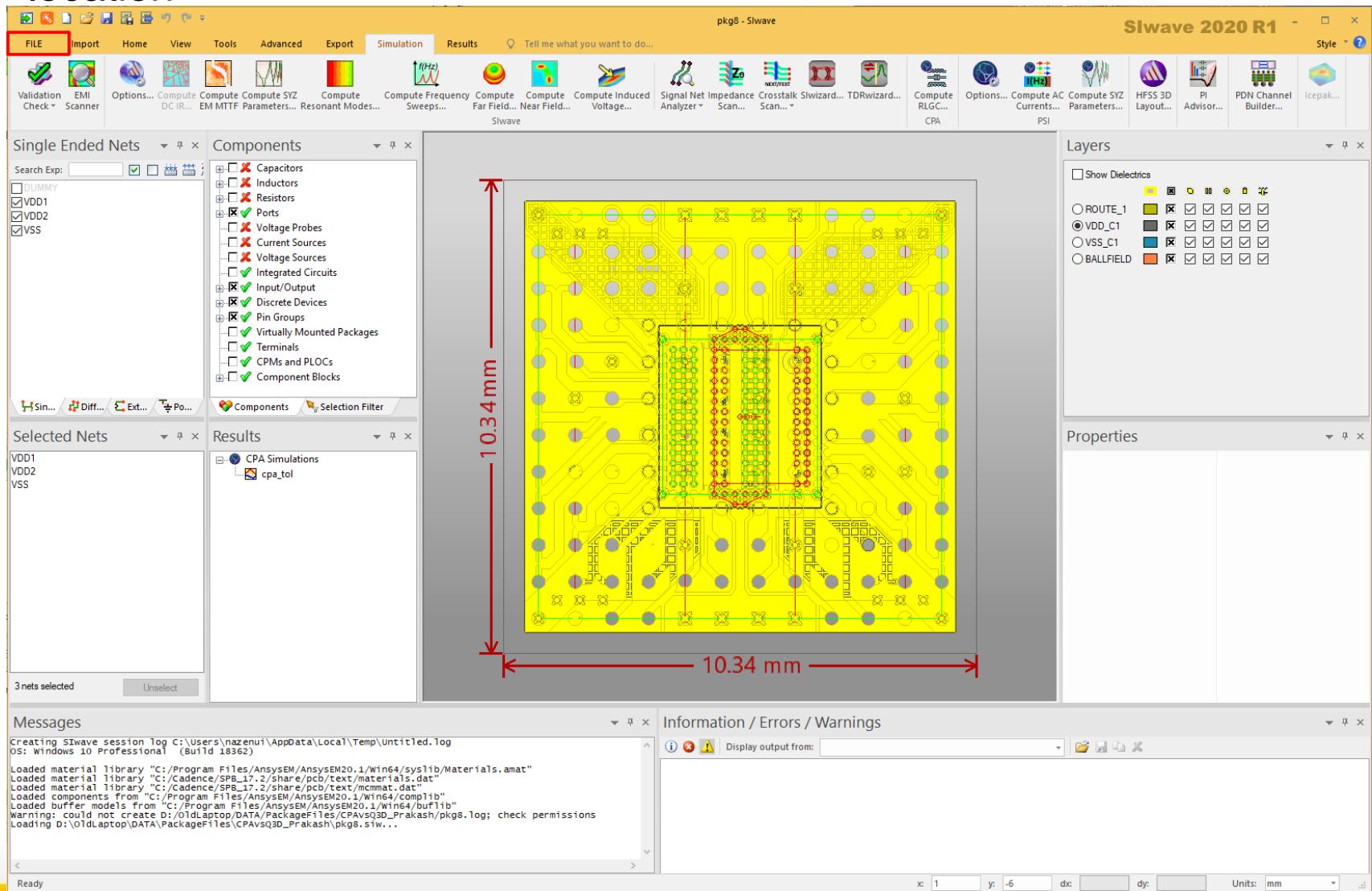

# Example 1- Package PDN extraction

- Open project file **pkg.siw** : **SIwave** -> **File** -> **Open** -> Browse to file location

# Example 1- Package PDN extraction

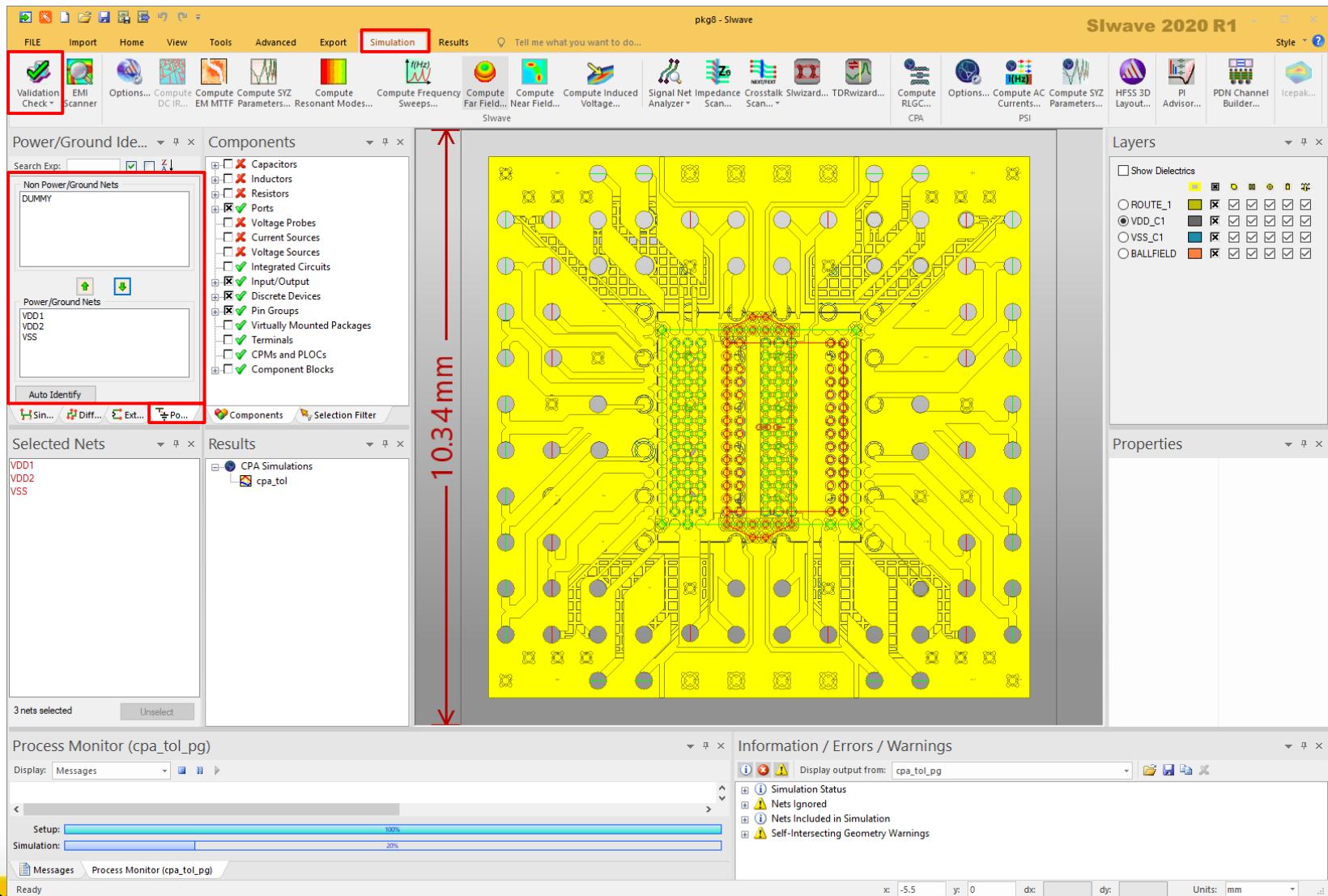

- Classify Power/Ground Nets accordingly

- Tools -> Sanitize Layout

- Simulation -> Validation Check

# Example 1- Package PDN extraction

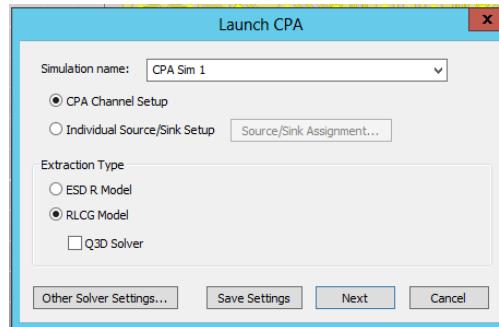

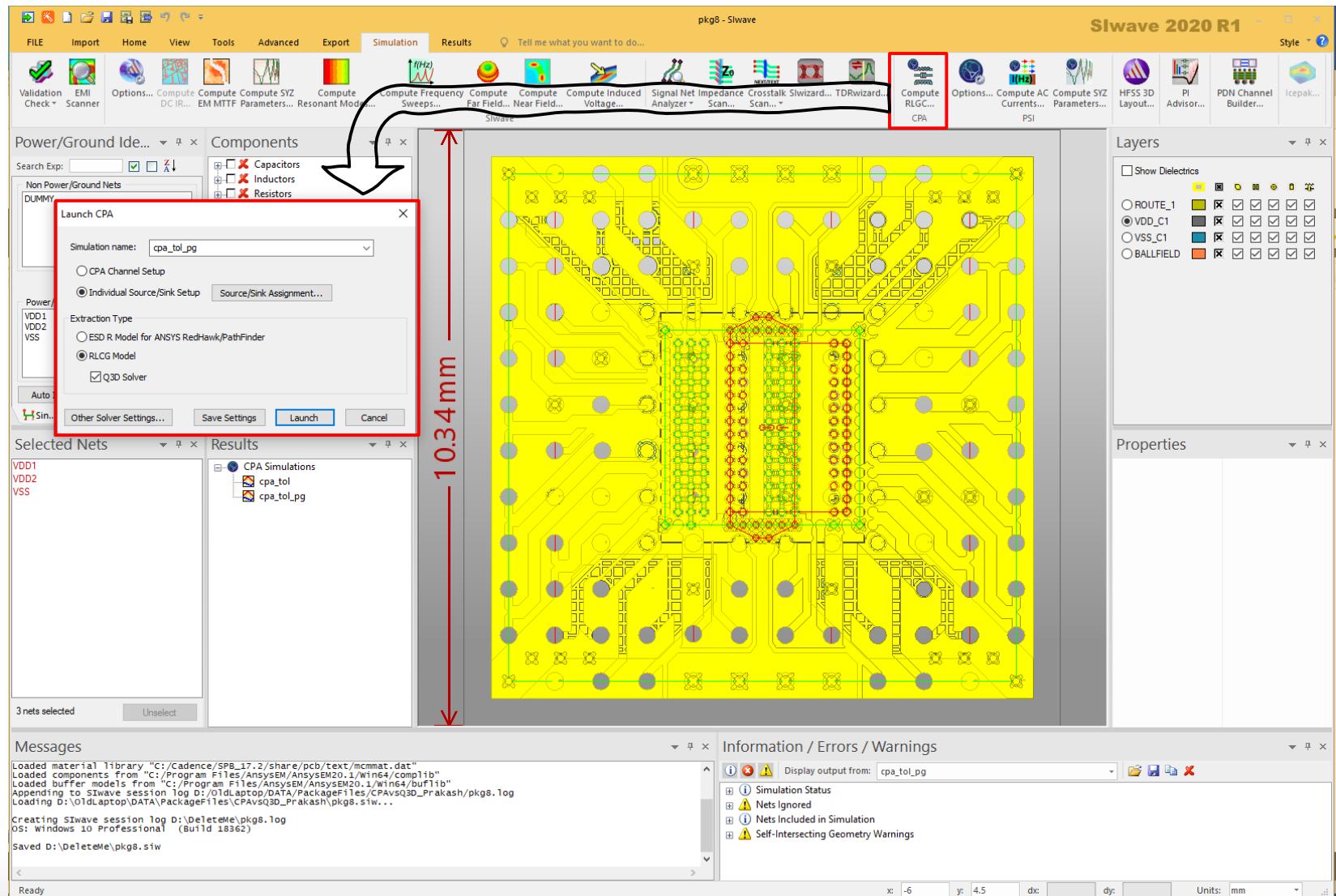

- Launch CPA interface: **Simulations -> Compute RLGC (CPA)**

# Example 1- Package PDN extraction

- Select **Individual Source/Sink Setup** option

- Click on the **Source/Sink Assignment** button, & assign **Node Type** as below

- Set **Extraction Type** (select **RLCG Model+Q3D Solver** for this example)

- **RLCG Model** only -> CPA fast FEM

- **Q3D Solver** -> Use Q3D MoM Solver with Adaptive Meshing

Pin Groups were previously defined

Source/Sink Assignment...

Extraction Type

Source

Sink

Float

Display Ports

Apply

Launch CPA

Simulation name: cpa\_tol

CPA Channel Setup

Individual Source/Sink Setup

Source/Sink Assignment...

ESD R Model for ANSYS RedHawk/PathFinder

RLCG Model

Q3D Solver

Other Solver Settings...

Save Settings

Launch

Cancel

Hide RLCs

Verify

OK

Cancel

3 & 4 Next slide

There must be at least a single source and sink for each net

Explanation: Schematic of this Setup

Sources

Nets

Sinks

Die

src1 — VDD1 — sk1

src2 — VSS — sk2 — BGA

src3 — VDD2 — sk3

| Net  | Node (Group)   | Component | Node Kind | Node Type |

|------|----------------|-----------|-----------|-----------|

| VDD2 | DIE_VDD2_GROUP | DIE       | Pin Group | Source    |

| VDD1 | DIE_VDD1_GROUP | DIE       | Pin Group | Source    |

| VSS  | DIE_VSS_GROUP  | DIE       | Pin Group | Source    |

| VDD1 | BGA_VDD1_GROUP | BGA       | Pin Group | Sink      |

| VDD2 | BGA_VDD2_GROUP | BGA       | Pin Group | Sink      |

| VSS  | BGA_VSS_GROUP  | BGA       | Pin Group | Sink      |

# Example 1- Package PDN extraction

- CPA Setup – Other Solver Settings & Launch simulations

- Under Net Processing, choose either custom or auto net selection

- Choose **Custom Net Selection** to include only Nets in the **Selected Nets** window in the simulation

- Specify AC solution frequency as **G+AC RL Frequency**

- Select desired **Parameters to Compute**

- Adjust **CG solver** and **RL solver** convergence settings

- Use **slider bar** for recommended settings for either SI or PI extraction

- Set Model Type to **IC** for RDL structures and **Package** or **PCB** for others

- In the **Multiprocessing tab**, set available #cores & HPC license

- The CPA setup options can be **exported** for subsequent reuse

- OK to complete setup. **Launch Simulation**

# Optionally, CPA Channel Setup Option

- **CPA Channel Setup** requires that all the components have the reference net (usually ground net) routed to them

# Example 1- Package PDN extraction

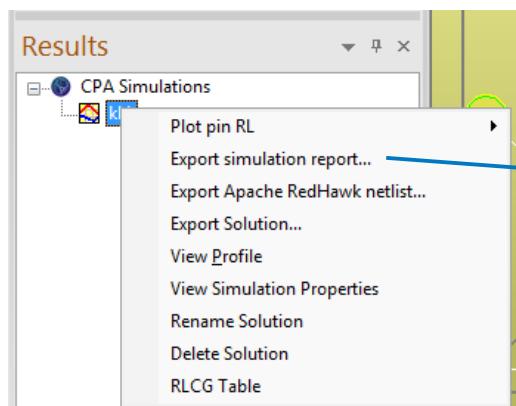

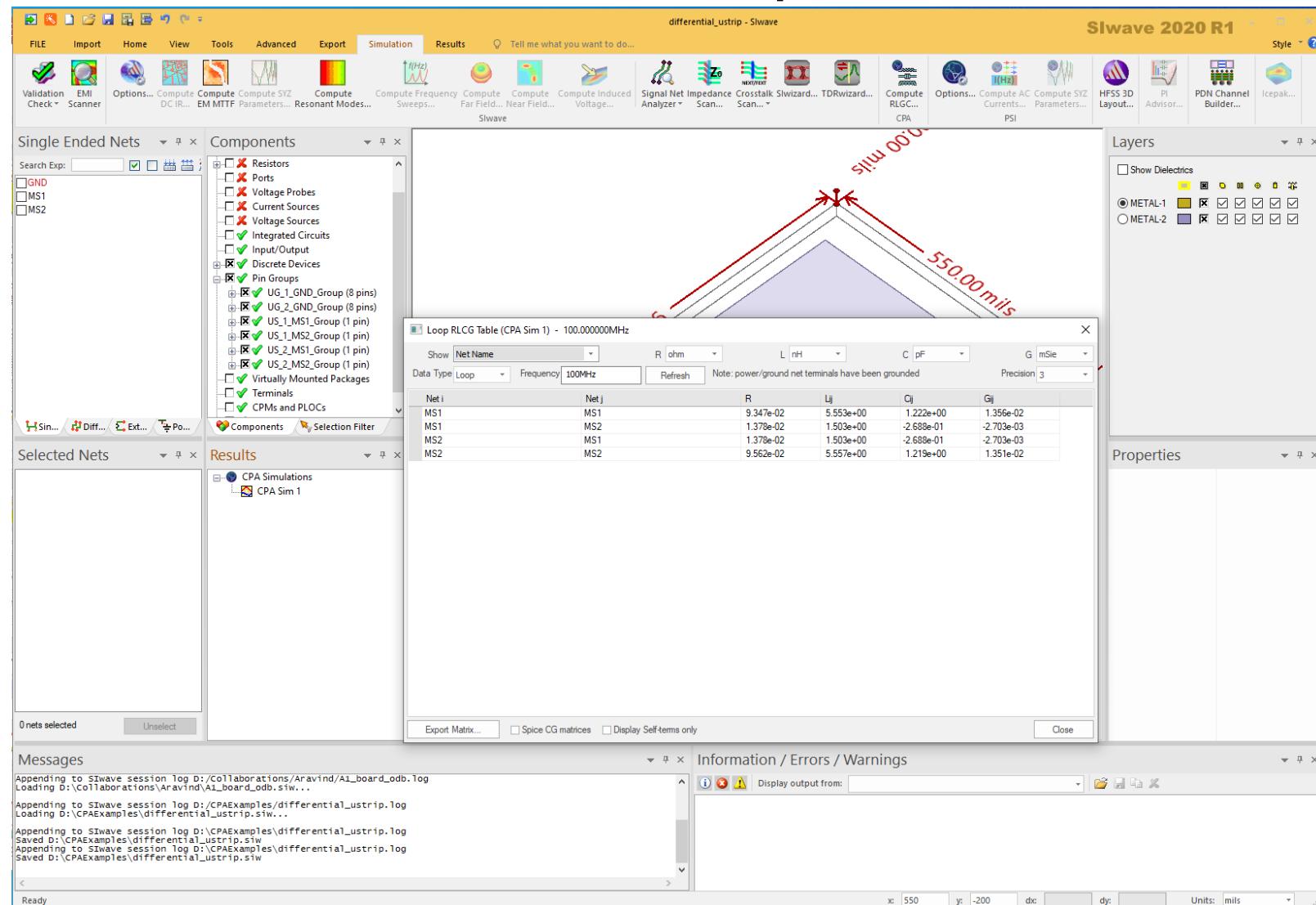

- Simulation Results – Partial and Loop RLCG values are generated

- RMC on the **Results** folder -> RLCG Table, Show **Net Name**, Data Type **Loop** – see below

The screenshot shows the Siwave 2020 R1 software interface. The main window displays a PCB layout with various components and vias. A red vertical line on the left indicates a dimension of 10.34 mm. The software interface includes the following panels:

- Components**: A tree view of the board components including Capacitors, Inductors, Resistors, Ports, Voltage Probes, Current Sources, Integrated Circuits, Input/Output, Discrete Devices, Pin Groups, Virtually Mounted Packages, Terminals, CPMs and PLOCs, and Component Blocks.

- Power/Ground Ide...**: A list of non-power/ground nets: DUMMY, Power/Ground Nets: VDD1, VDD2, VSS, and an Auto Identify button.

- Selected Nets**: A list of selected nets: VDD1, VDD2, VSS.

- Results**: A tree view showing CPA Simulations, cpa\_tol, and cpa\_tol\_pg. The cpa\_tol\_pg node is expanded, showing options like Plot pin RL, Export simulation report..., Export ANSYS RedHawk netlist..., Export Solution..., View Profile, View Simulation Properties, Rename Solution, Delete Solution, RLCG Table, and Remap PLOC/CPM. The RLCG Table option is highlighted with a red box.

- Layers**: A panel showing layer settings for various components like ROUTE\_1, VDD\_C1, VSS\_C1, and BALLFIELD.

- Loop RLCG Table (cpa\_tol\_pg) - 100.000000MHz**: A table showing loop values. The table has columns for Net i, Net j, R (ohm), L (nH), C (pF), and G (mSIE). The data is as follows:

| Net i | Net j | R         | L         | C          | G          |

|-------|-------|-----------|-----------|------------|------------|

| VDD1  | VDD1  | 2.116e-03 | 5.892e-02 | 3.750e+01  | 7.558e-01  |

| VDD1  | VDD2  | 8.537e-04 | 2.294e-02 | -2.165e+00 | -4.300e-02 |

| VDD2  | VDD1  | 8.537e-04 | 2.294e-02 | -2.165e+00 | -4.300e-02 |

| VDD2  | VDD2  | 1.924e-02 | 5.968e-01 | 3.930e+00  | 6.901e-02  |

At the bottom, there are buttons for Export Matrix..., Spice CG matrices, and Display Self-terms only. The status bar shows coordinates x: -6.5, y: 5, dx: , dy: , Units: mm.

- Loop values are based on defining **VSS** as the return path

- Obtain results at interpolated points by changing **Frequency** value

# Simulation Results for various Solvers

SIwave RLCG Model Only -- aka CPA fast FEM

| Net i | Net j | R <sub>ij</sub> (mΩ) | L <sub>ij</sub> (nH) | C <sub>ij</sub> (pF) | G <sub>ij</sub> (mSie) |

|-------|-------|----------------------|----------------------|----------------------|------------------------|

| VDD1  | VDD1  | 2.081                | 0.06831              | 32.39                | 0.6682                 |

| VDD2  | VDD2  | 24.260               | 0.4602               | 3.755                | 0.06701                |

Comments

**Total:**

**0m53s**

Fastest & Accurate

SIwave RLCG Model +Q3D Solver -- aka CPA MoM

| Net i | Net j | R <sub>ij</sub> (mΩ) | L <sub>ij</sub> (nH) | C <sub>ij</sub> (pF) | G <sub>ij</sub> (mSie) |

|-------|-------|----------------------|----------------------|----------------------|------------------------|

| VDD1  | VDD1  | 2.107                | 0.05892              | 35.700               | 0.75420                |

| VDD2  | VDD2  | 19.210               | 0.59680              | 3.717                | 0.06754                |

**Total:**

**14m44s**

Fast & More Accurate

Q3D Standalone

| Net i | Net j | R <sub>ij</sub> (mΩ) | L <sub>ij</sub> (nH) | C <sub>ij</sub> (pF) | G <sub>ij</sub> (mSie) |

|-------|-------|----------------------|----------------------|----------------------|------------------------|

| VDD1  | VDD1  | 2.0466               | 0.054864             | 36.153               | 0.76444                |

| VDD2  | VDD2  | 17.716               | 0.57016              | 3.741                | 0.067852               |

**Total:**

**51m12s**

Standard for Accuracy

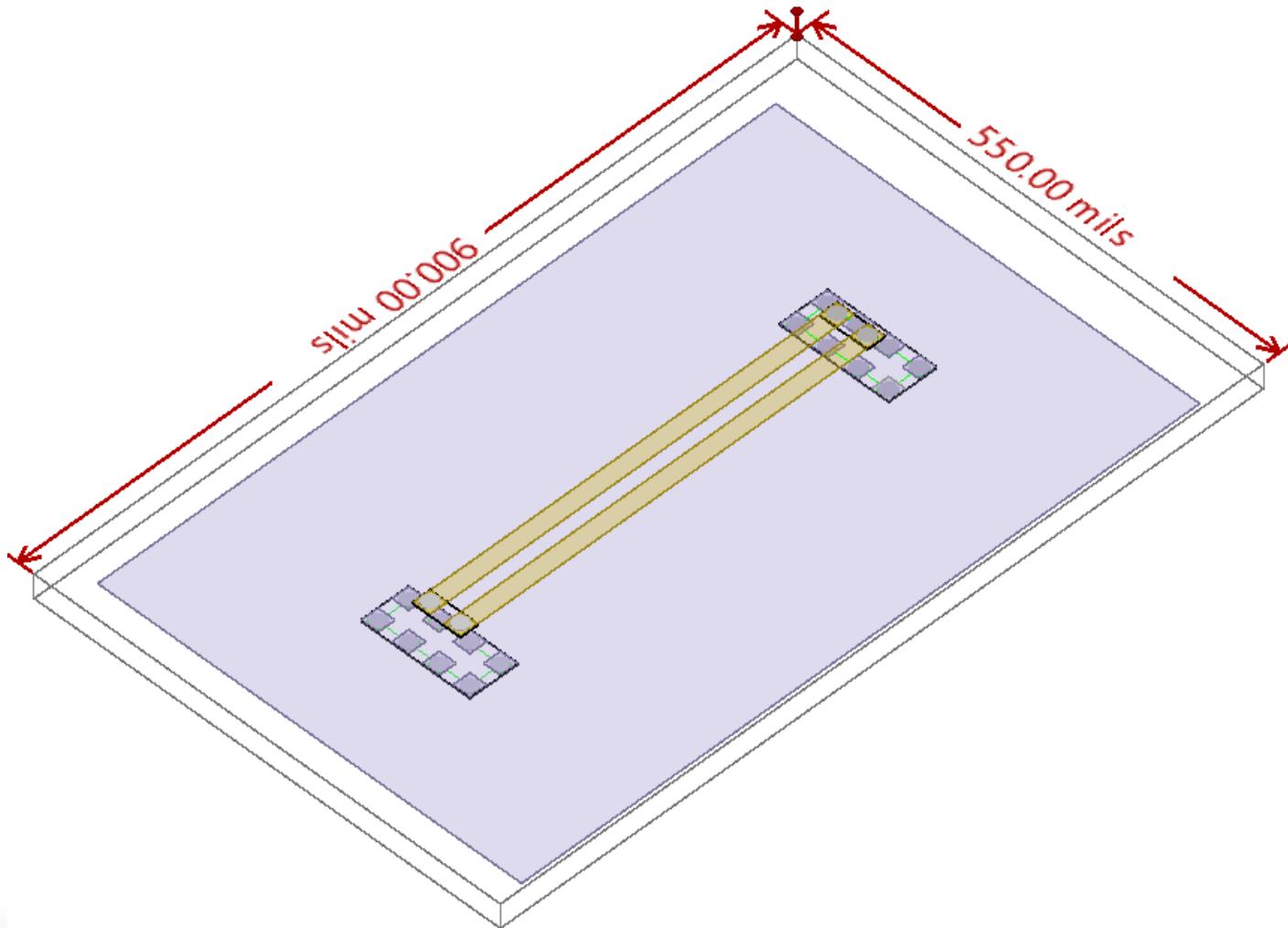

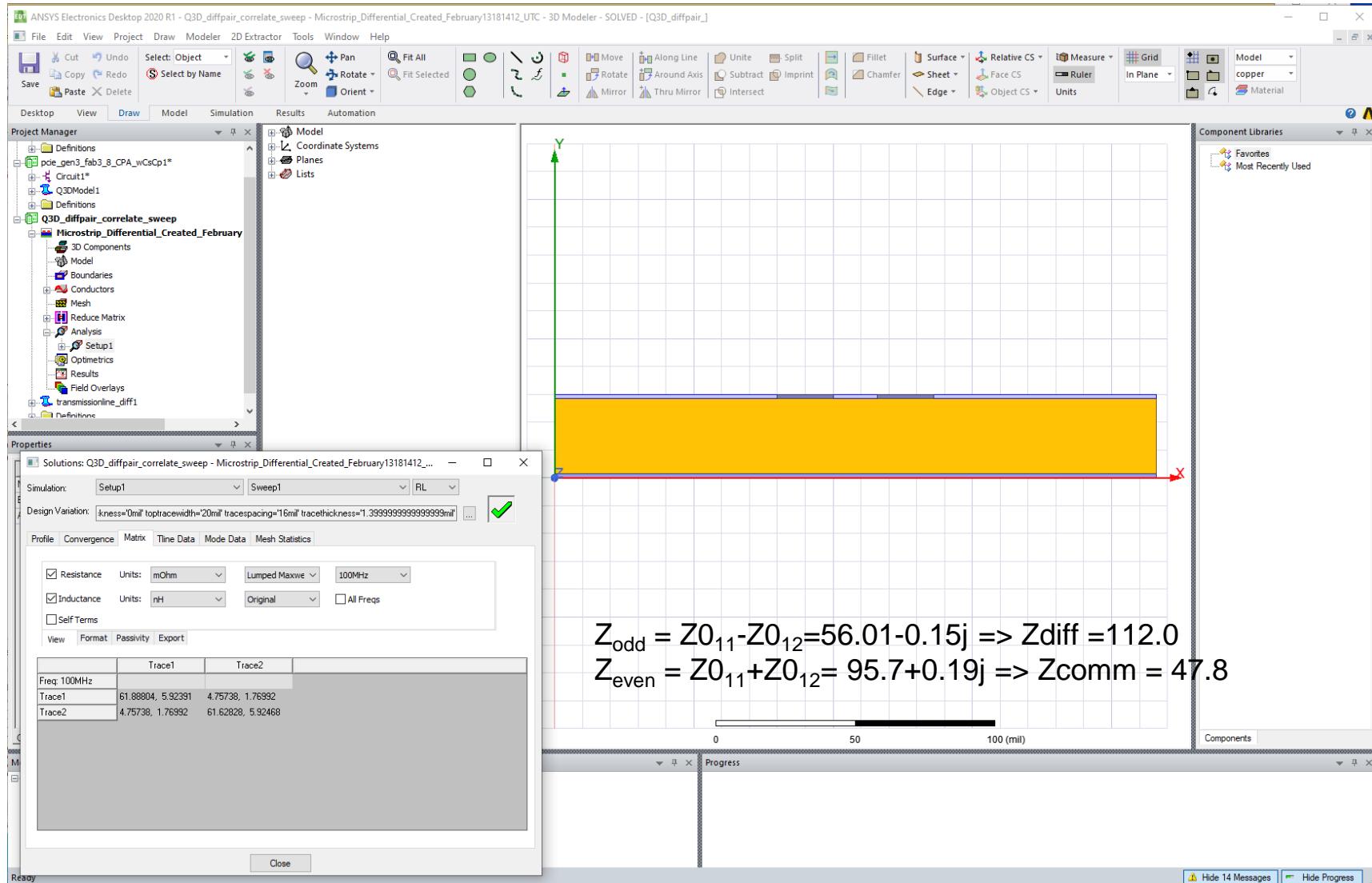

# Example 2: Differential Pair Example

- Open project file **differential\_ustrip.siw**

- **SIwave** -> **File** -> **Open** -> Browse to file location

- Select Individual Source/Sink Setup -> Source/Sink Assignment and setup sources and sinks as shown below

- Launch **Other Solver Settings** and configure the options – see below

- Setup the **NetProcessing** (choose **auto** option) & **Multiprocessing** tabs

- OK to complete setup. **Launch Simulation**

# Simulation Results & Interpretation

$$Z_{\text{odd}} = \sqrt{(L_{11} - L_{12}) / (C_{11} - C_{12})} = 52.12 \Rightarrow Z_{\text{diff}} = 2 * Z_{\text{odd}} = 104.24$$

$$Z_{\text{even}} = \sqrt{(L_{11} + L_{12}) / (C_{11} + C_{12})} = 86.04 \Rightarrow Z_{\text{comm}} = (1/2) * Z_{\text{even}} = 43.02$$

# Comparison with 2D Extractor

- Run the 2D Extractor simulation included and review the results

- Comparing 2D Extractor vs Q3D results  $Z_{\text{diff}} = 112.0$  vs 104.2 and  $Z_{\text{comm}} = 47.8$  vs 43.0

# Conclusion of 2D Extractor vs Q3D

For this example

- The difference in results between 2D Extractor and Q3D in this example is due to the edge effects that exist in the Q3D model

- Remember that the 2D Extractor extract the per-unit-length parameters assuming an infinitely long transmission line

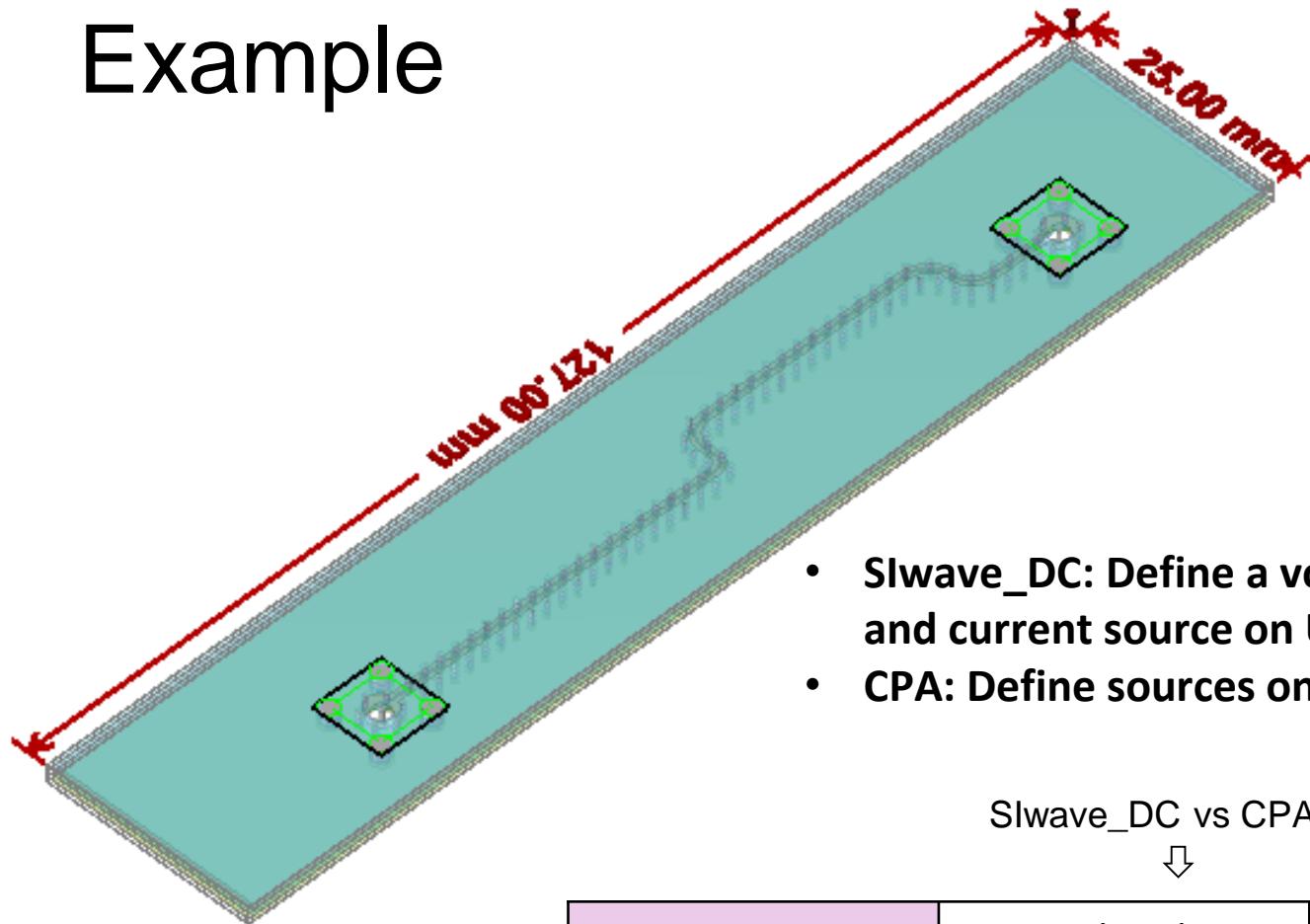

# Extra: Transmission line Extraction Example

- **SIwave\_DC:** Define a voltage source on U10 and current source on U11

- **CPA:** Define sources on U10 and sinks on U11

SIwave\_DC vs CPA

| @DC       | R (mΩ) | L (nH) |

|-----------|--------|--------|

| SIwave DC | 158.39 | 78.29  |

| CPA       | 158.30 | 78.13  |