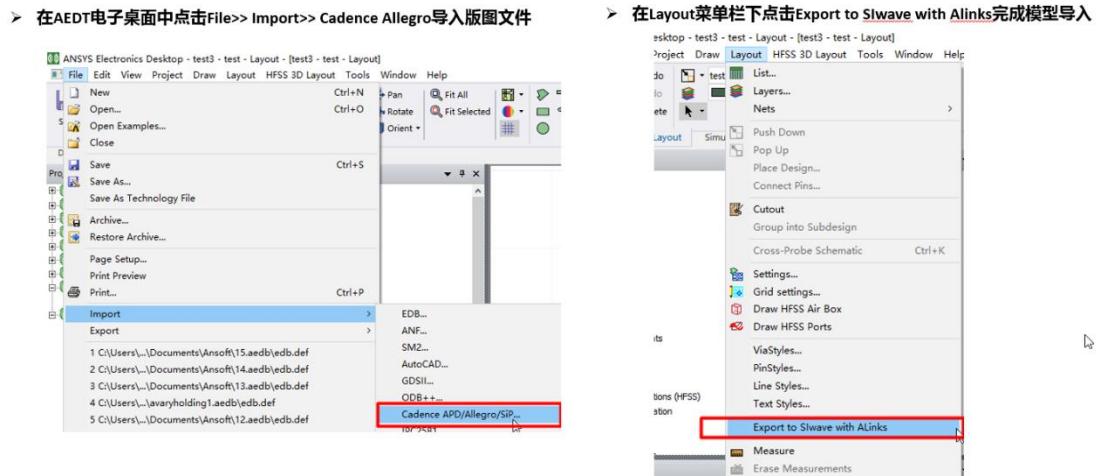

## Q1. R19.2 版本后，如何将 cadence allegro 的版图文件导入到 Siwave?

答：R19.2 版本之后的 Siwave 导入 Allegro 的接口被关闭了，目前的导入流程多了一步，需要先将版图导入到 HFSS 3D layout 中，再导入到 Siwave，具体操作如下图所示

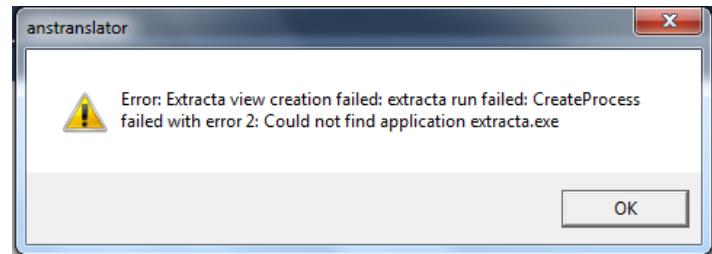

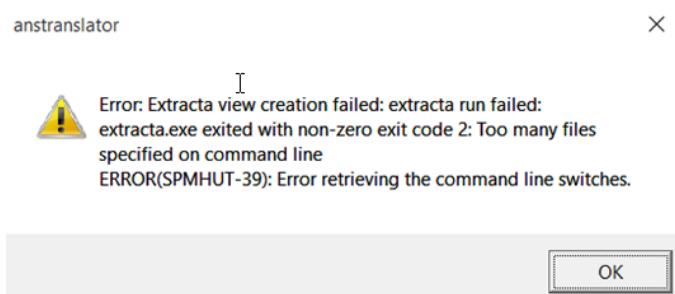

## Q2. Siwave/HFSS 3D layout 导入 cadence allegro 版图文件报错问题解决方法?

答：a. 首先如下图所示，当提示 Could not find application extracta.exe 时，请确认本机是否安装 cadence allegro 工具，请先安装后再导入

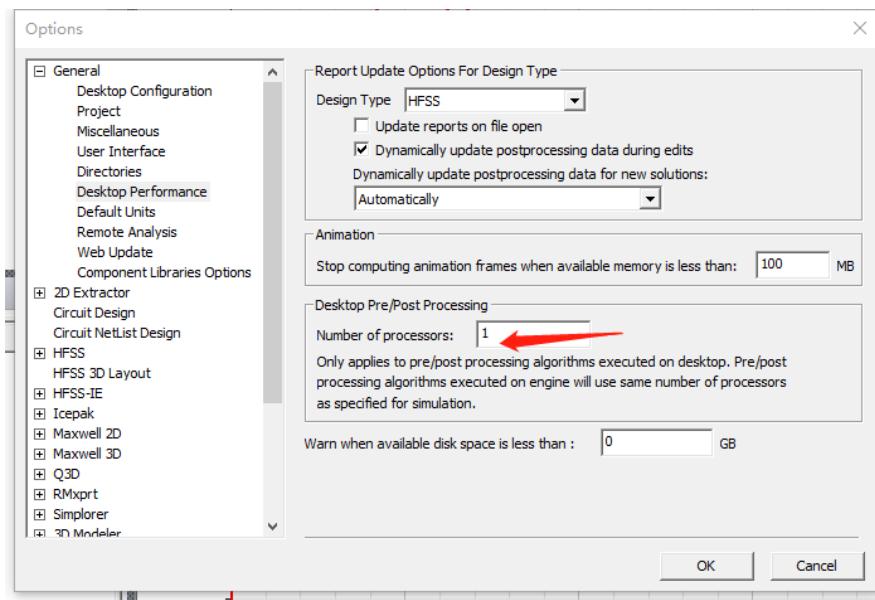

b. 如果提示 Too many files specified on command line，请将下图 options 窗口中的 Desktop performance>> Number of processors 中的数字改为 2，这个问题在 R19.2 后被修复了，所以遇到这个问题时，也可以直接升级 ANSYS 软件

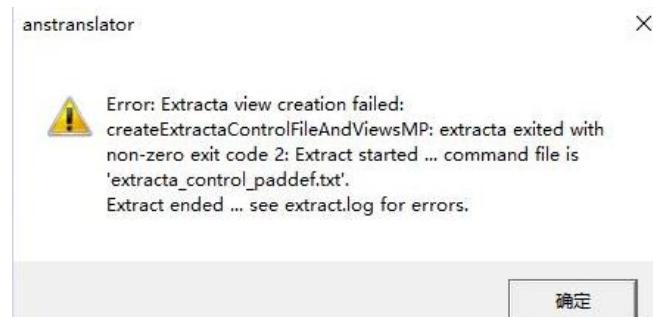

c. 如果提示 extracta exited with non-zero exit code2: Extract started... 请下载安装最新的 cadence hotfix 或者升级 cadence allegro，比如从 Allegro 16.6 升级到 17.2。

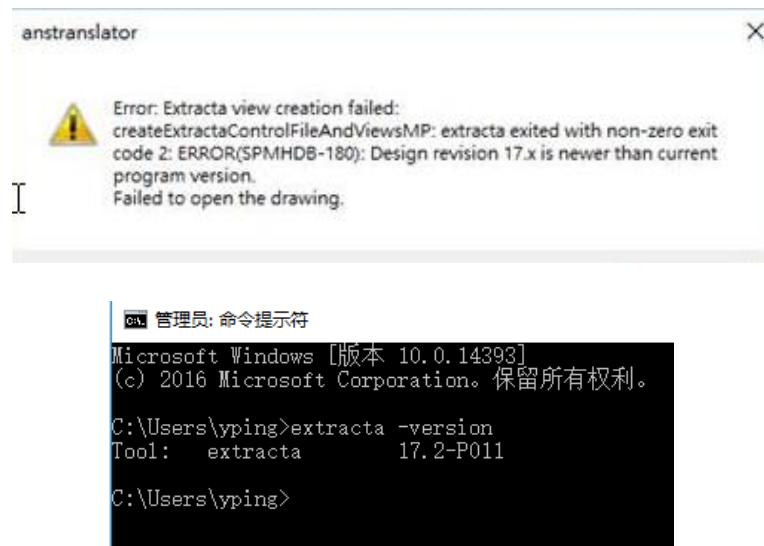

d. 如果提示 Design revision 17.x is newer than current program version... 即当前版图文件的版本高于 extracta.exe 的版本，需要安装 cadence allegro 17.2。查看 extracta.exe 版本的方法如下图所示，打开 cmd 输入 extracta -version

安装完 cadence allegro 17.2 后，为了确保 extracta.exe 工作在当前版本下，需要添加环境变量，然后重启电脑。假如 Cadence 17.2 被安装在 C 盘，则需要在环境变量 PATH 下添加如下路径：

```

C:\Cadence\SPB_17.2\openaccess\bin\x64\opt;

C:\Cadence\SPB_17.2\tools\capture;

C:\Cadence\SPB_17.2\tools\pspice;

C:\Cadence\SPB_17.2\tools\spectre\bin;

C:\Cadence\SPB_17.2\tools\fet\bin;

C:\Cadence\SPB_17.2\tools\libutil\bin;

C:\Cadence\SPB_17.2\tools\bin;

C:\Cadence\SPB_17.2\tools\pcb\bin;

```

e. 版图文件尽量放在本地导入，不要通过局域网路径导入